EM78P312N

8-Bit Microcontroller

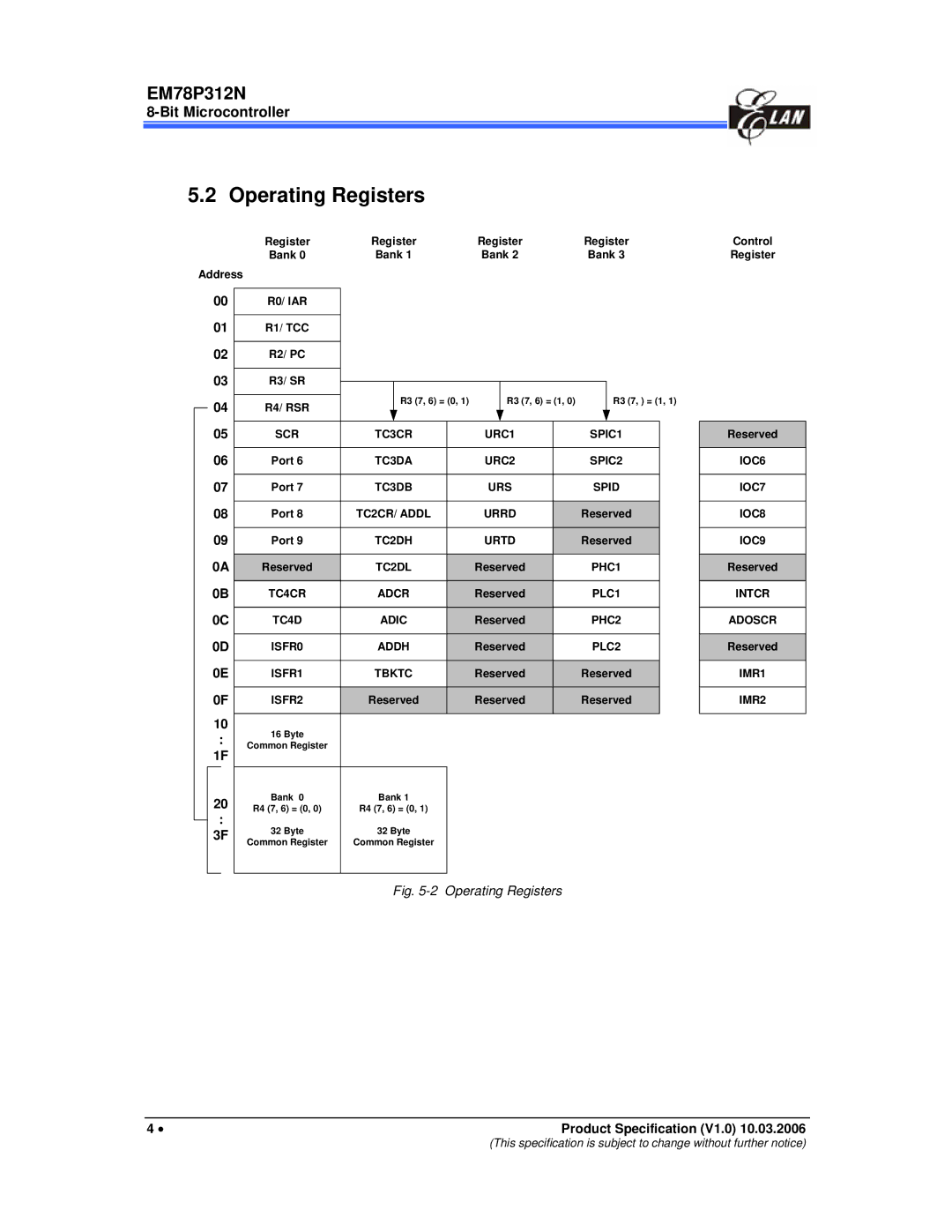

5.2 Operating Registers

| Register | Register | Register | Register |

| Bank 0 | Bank 1 | Bank 2 | Bank 3 |

Address |

|

|

|

|

00 | R0/ IAR |

|

|

|

01 | R1/ TCC |

|

|

|

02 | R2/ PC |

|

|

|

03 | R3/ SR |

|

|

|

04 | R4/ RSR | R3 (7, 6) = (0, 1) | R3 (7, 6) = (1, 0) | R3 (7, ) = (1, 1) |

|

|

| ||

05 | SCR | TC3CR | URC1 | SPIC1 |

06 | Port 6 | TC3DA | URC2 | SPIC2 |

07 | Port 7 | TC3DB | URS | SPID |

08 | Port 8 | TC2CR/ ADDL | URRD | Reserved |

09 | Port 9 | TC2DH | URTD | Reserved |

0A | Reserved | TC2DL | Reserved | PHC1 |

0B | TC4CR | ADCR | Reserved | PLC1 |

0C | TC4D | ADIC | Reserved | PHC2 |

0D | ISFR0 | ADDH | Reserved | PLC2 |

0E | ISFR1 | TBKTC | Reserved | Reserved |

0F | ISFR2 | Reserved | Reserved | Reserved |

10 | 16 Byte |

|

|

|

: |

|

|

| |

Common Register |

|

|

| |

1F |

|

|

|

|

20 | Bank 0 | Bank 1 |

|

|

R4 (7, 6) = (0, 0) | R4 (7, 6) = (0, 1) |

|

| |

: | 32 Byte | 32 Byte |

|

|

3F |

|

| ||

Common Register | Common Register |

|

| |

|

|

|

Fig. 5-2 Operating Registers

Control

Register

Reserved

IOC6

IOC7

IOC8

IOC9

Reserved

INTCR

ADOSCR

Reserved

IMR1

IMR2

4 • | Product Specification (V1.0) 10.03.2006 |

(This specification is subject to change without further notice)