EM78P312N

8-Bit Microcontroller

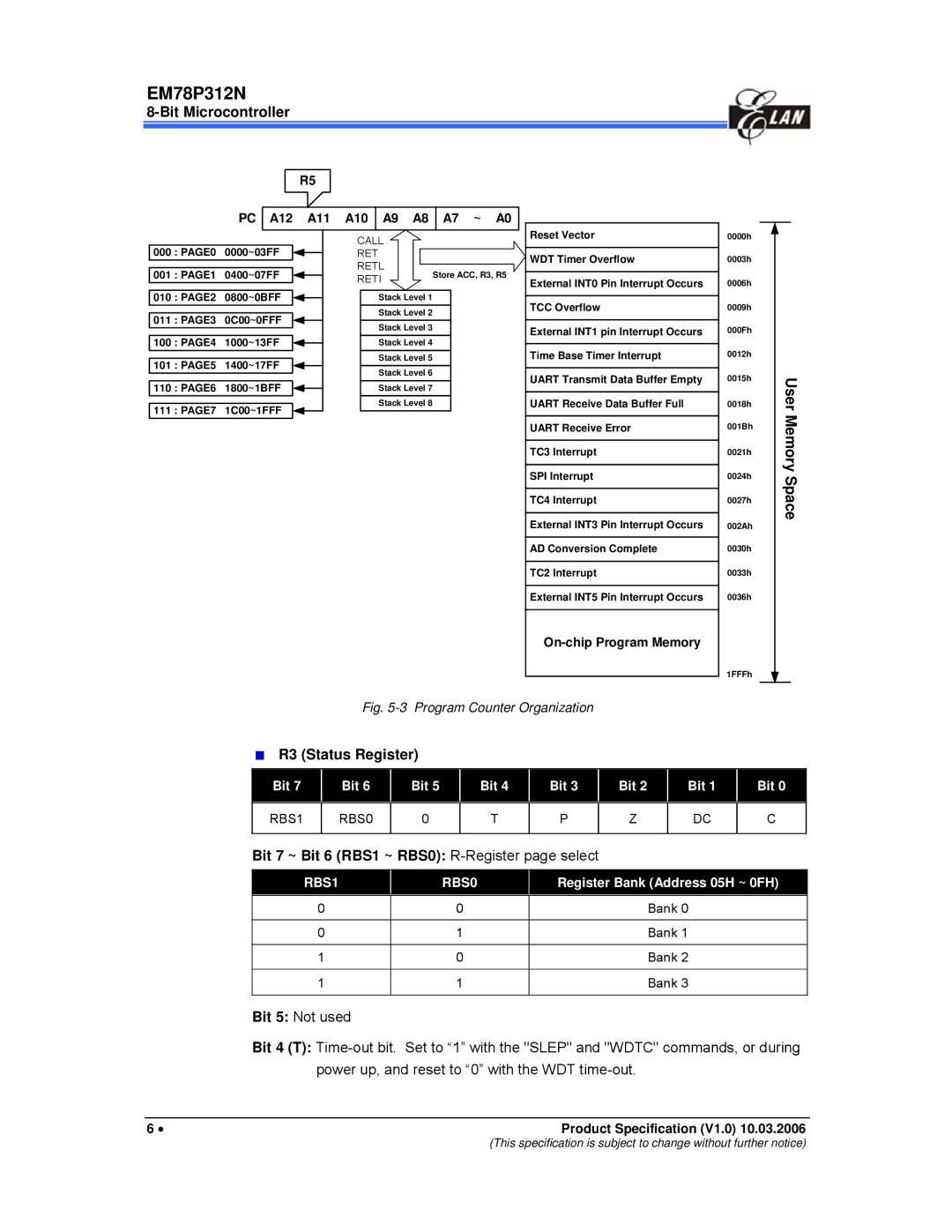

R5

PC A12 A11 A10 A9 A8 A7 ~ A0

000 : PAGE0 0000~03FF

001 : PAGE1 0400~07FF

010 : PAGE2 0800~0BFF

011 : PAGE3 0C00~0FFF

100 : PAGE4 1000~13FF

101 : PAGE5 1400~17FF

110 : PAGE6 1800~1BFF

111 : PAGE7 1C00~1FFF

CALL

RET

RETL

RETI | Store ACC, R3, R5 |

Stack Level 1

Stack Level 2

Stack Level 3

Stack Level 4

Stack Level 5

Stack Level 6

Stack Level 7

Stack Level 8

Reset Vector

WDT Timer Overflow

External INT0 Pin Interrupt Occurs

TCC Overflow

External INT1 pin Interrupt Occurs

Time Base Timer Interrupt

UART Transmit Data Buffer Empty

UART Receive Data Buffer Full

UART Receive Error

TC3 Interrupt

SPI Interrupt

TC4 Interrupt

External INT3 Pin Interrupt Occurs

AD Conversion Complete

TC2 Interrupt

External INT5 Pin Interrupt Occurs

On-chip Program Memory

0000h

0003h

0006h

0009h

000Fh

0012h

0015h

0018h

001Bh

0021h

0024h

0027h

002Ah

0030h

0033h

0036h

1FFFh

User Memory Space

Fig. 5-3 Program Counter Organization

R3 (Status Register)

Bit 7 | Bit 6 | Bit 5 | Bit 4 |

|

|

|

|

Bit 3

Bit 2 | Bit 1 | Bit 0 |

|

|

|

RBS1

RBS0

0

T

P

Z

DC

C

Bit 7 ~ Bit 6 (RBS1 ~ RBS0): R-Register page select

RBS1 |

| RBS0 |

| Register Bank (Address 05H ~ 0FH) |

|

|

|

|

|

|

|

0 |

| 0 |

| Bank 0 | |

|

|

|

|

| |

0 |

| 1 |

| Bank 1 | |

|

|

|

|

| |

1 |

| 0 |

| Bank 2 | |

|

|

|

|

| |

1 |

| 1 |

| Bank 3 | |

|

|

|

|

|

|

Bit 5: Not used

Bit 4 (T):

6 • | Product Specification (V1.0) 10.03.2006 |

(This specification is subject to change without further notice)