EM78P312N

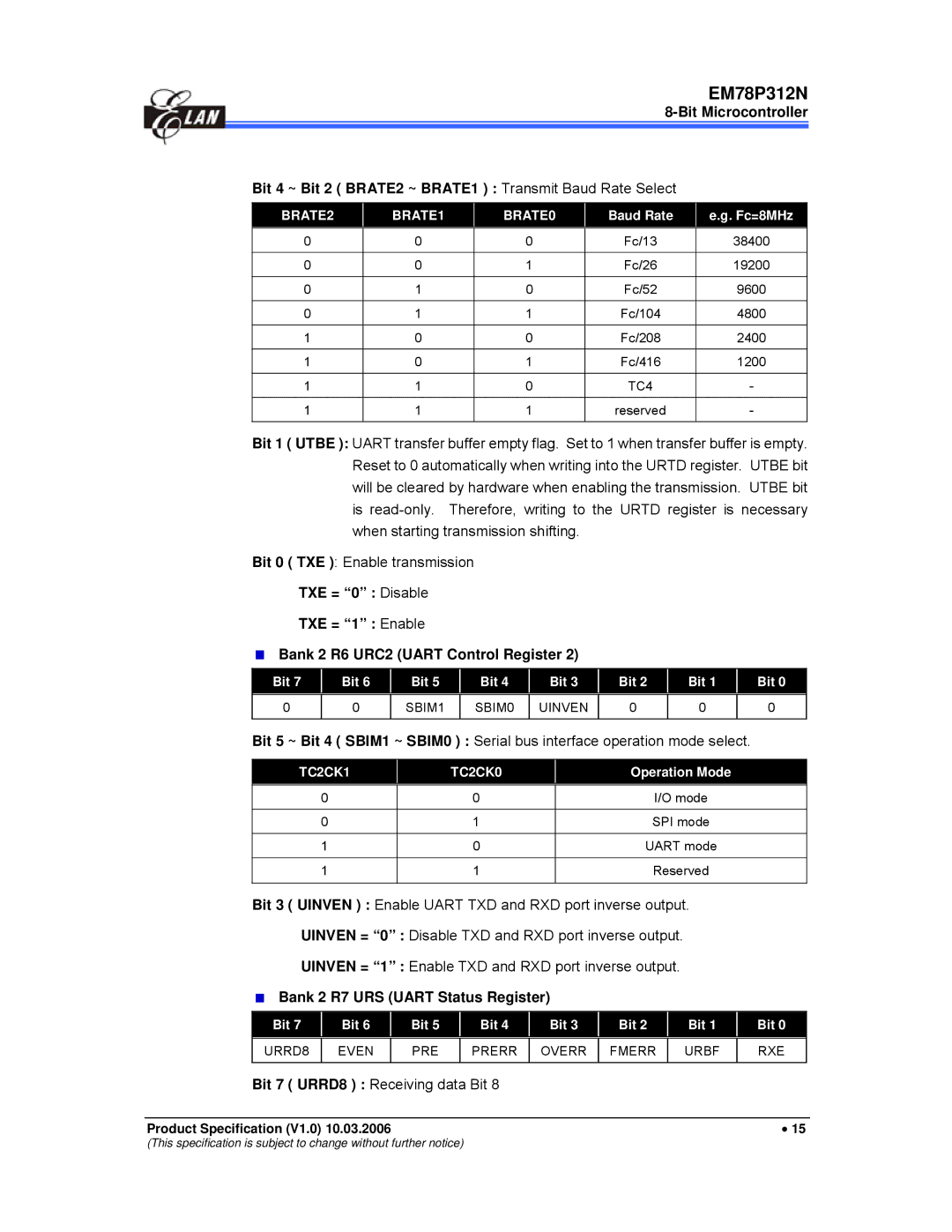

Bit 4 ~ Bit 2 ( BRATE2 ~ BRATE1 ) : Transmit Baud Rate Select

BRATE2 |

| BRATE1 |

| BRATE0 |

| Baud Rate |

| e.g. Fc=8MHz |

0 |

| 0 |

| 0 |

| Fc/13 |

| 38400 |

|

|

|

|

|

|

|

|

|

0 |

| 0 |

| 1 |

| Fc/26 |

| 19200 |

|

|

|

|

|

|

|

|

|

0 |

| 1 |

| 0 |

| Fc/52 |

| 9600 |

0 |

| 1 |

| 1 |

| Fc/104 |

| 4800 |

|

|

|

|

|

|

|

|

|

1 |

| 0 |

| 0 |

| Fc/208 |

| 2400 |

|

|

|

|

|

|

|

|

|

1 |

| 0 |

| 1 |

| Fc/416 |

| 1200 |

|

|

|

|

|

|

|

|

|

1 |

| 1 |

| 0 |

| TC4 |

| - |

|

|

|

|

|

|

|

|

|

1 |

| 1 |

| 1 |

| reserved |

| - |

|

|

|

|

|

|

|

|

|

Bit 1 ( UTBE ): UART transfer buffer empty flag. Set to 1 when transfer buffer is empty. Reset to 0 automatically when writing into the URTD register. UTBE bit will be cleared by hardware when enabling the transmission. UTBE bit is

Bit 0 ( TXE ): Enable transmission

TXE = “0” : Disable

TXE = “1” : Enable

Bank 2 R6 URC2 (UART Control Register 2)

Bit 7 | Bit 6 | Bit 5 | Bit 4 |

|

|

|

|

Bit 3

Bit 2 | Bit 1 | Bit 0 |

|

|

|

0

0

SBIM1

SBIM0 UINVEN

0

0

0

Bit 5 ~ Bit 4 ( SBIM1 ~ SBIM0 ) : Serial bus interface operation mode select.

TC2CK1 |

| TC2CK0 |

| Operation Mode |

0 |

| 0 |

| I/O mode |

|

|

|

|

|

0 |

| 1 |

| SPI mode |

|

|

|

|

|

1 |

| 0 |

| UART mode |

|

|

|

|

|

1 |

| 1 |

| Reserved |

|

|

|

|

|

Bit 3 ( UINVEN ) : Enable UART TXD and RXD port inverse output. UINVEN = “0” : Disable TXD and RXD port inverse output. UINVEN = “1” : Enable TXD and RXD port inverse output.

Bank 2 R7 URS (UART Status Register)

Bit 7 | Bit 6 | Bit 5 | Bit 4 |

|

|

|

|

Bit 3

Bit 2 | Bit 1 | Bit 0 |

URRD8

EVEN

PRE

PRERR OVERR FMERR

URBF

RXE

Bit 7 ( URRD8 ) : Receiving data Bit 8

Product Specification (V1.0) 10.03.2006 | • 15 |

(This specification is subject to change without further notice)