EM78P312N

8-Bit Microcontroller

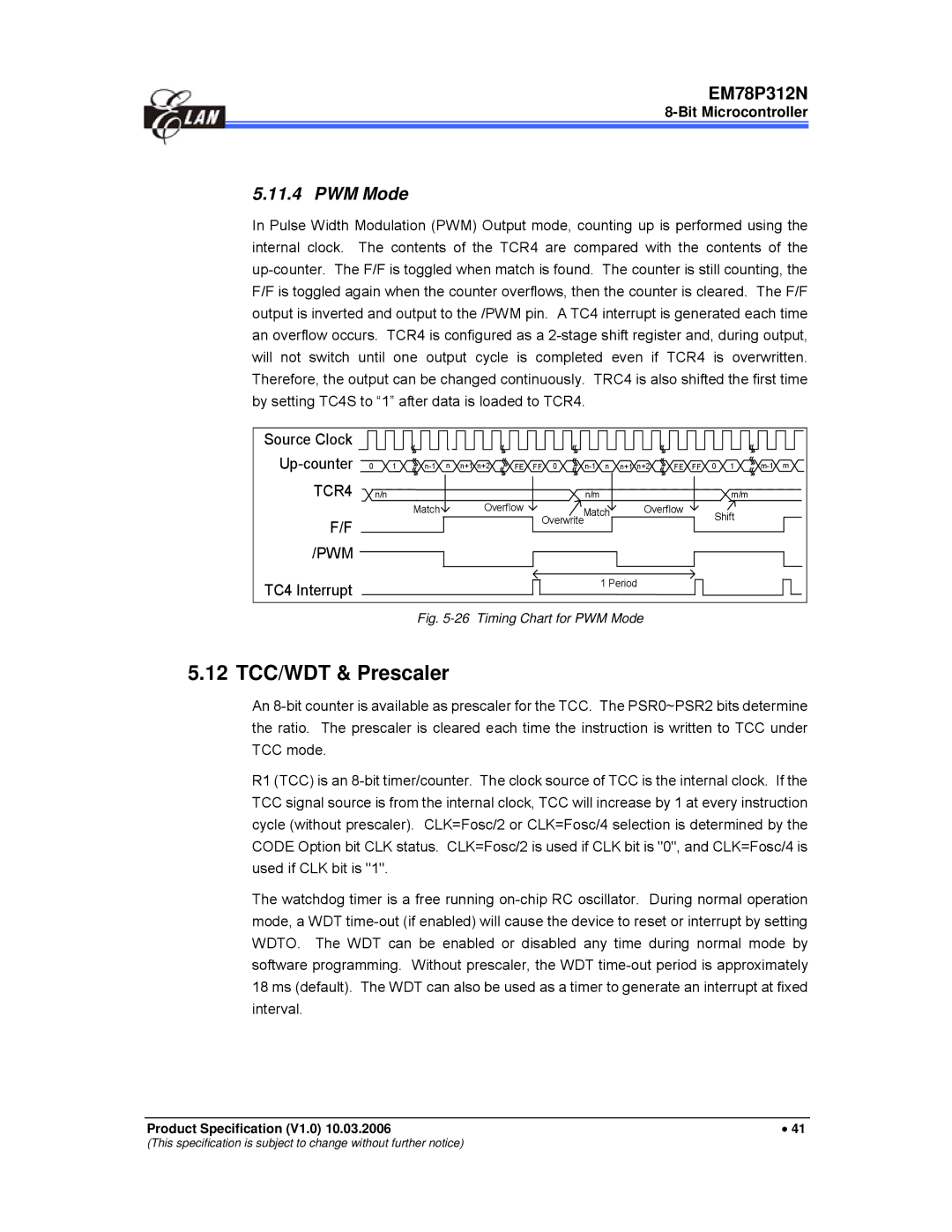

5.11.4 PWM Mode

In Pulse Width Modulation (PWM) Output mode, counting up is performed using the internal clock. The contents of the TCR4 are compared with the contents of the

Source Clock |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| 0 | 1 | n | n+1 n+2 | FE | FF 0 | n | n+1 n+2 | FE | FF | 0 | 1 | m | |||

TCR4 |

| n/n |

|

| Overflow |

| n/m |

|

|

|

|

| m/m |

|

| |

|

|

| Match |

|

| Match | Overflow |

| Shift |

|

| |||||

F/F |

|

|

|

|

|

| Overwrite |

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

/PWM |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

TC4 Interrupt |

|

|

|

|

|

|

|

| 1 Period |

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

Fig. 5-26 Timing Chart for PWM Mode

5.12 TCC/WDT & Prescaler

An

R1 (TCC) is an

The watchdog timer is a free running

Product Specification (V1.0) 10.03.2006 | • 41 |

(This specification is subject to change without further notice)