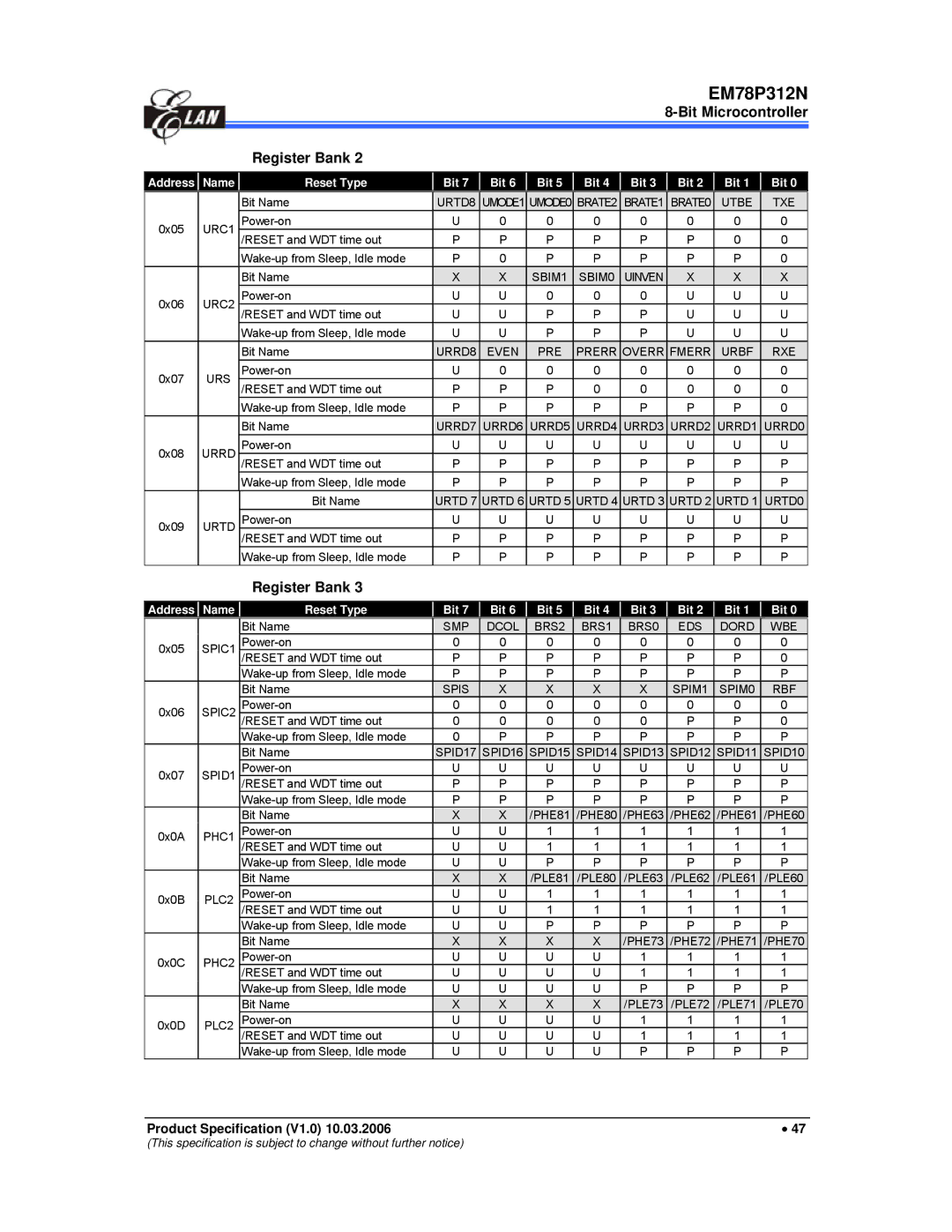

EM78P312N

8-Bit Microcontroller

Register Bank 2

Address |

| Name |

| Reset Type | Bit 7 |

| Bit 6 |

| Bit 5 |

| Bit 4 |

| Bit 3 |

| Bit 2 |

| Bit 1 |

| Bit 0 |

|

|

|

| Bit Name | URTD8 |

| UMODE1 |

| UMODE0 |

| BRATE2 |

| BRATE1 |

| BRATE0 |

| UTBE |

| TXE |

0x05 |

| URC1 |

| U |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 | |

| /RESET and WDT time out | P |

| P |

| P |

| P |

| P |

| P |

| 0 |

| 0 | |||

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

| P |

| 0 |

| P |

| P |

| P |

| P |

| P |

| 0 | |

|

|

|

| Bit Name | X |

| X |

| SBIM1 |

| SBIM0 |

| UINVEN |

| X |

| X |

| X |

0x06 |

| URC2 |

| U |

| U |

| 0 |

| 0 |

| 0 |

| U |

| U |

| U | |

| /RESET and WDT time out | U |

| U |

| P |

| P |

| P |

| U |

| U |

| U | |||

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

| U |

| U |

| P |

| P |

| P |

| U |

| U |

| U | |

|

|

|

| Bit Name | URRD8 |

| EVEN |

| PRE |

| PRERR |

| OVERR |

| FMERR |

| URBF |

| RXE |

0x07 |

| URS |

| U |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 | |

| /RESET and WDT time out | P |

| P |

| P |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 | |||

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

| P |

| P |

| P |

| P |

| P |

| P |

| P |

| 0 | |

|

|

|

| Bit Name | URRD7 |

| URRD6 |

| URRD5 |

| URRD4 |

| URRD3 |

| URRD2 |

| URRD1 |

| URRD0 |

0x08 |

| URRD |

| U |

| U |

| U |

| U |

| U |

| U |

| U |

| U | |

| /RESET and WDT time out | P |

| P |

| P |

| P |

| P |

| P |

| P |

| P | |||

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

| P |

| P |

| P |

| P |

| P |

| P |

| P |

| P | |

|

|

|

| Bit Name | URTD 7 |

| URTD 6 |

| URTD 5 |

| URTD 4 |

| URTD 3 |

| URTD 2 |

| URTD 1 |

| URTD0 |

0x09 |

| URTD | U |

| U |

| U |

| U |

| U |

| U |

| U |

| U | ||

/RESET and WDT time out | P |

| P |

| P |

| P |

| P |

| P |

| P |

| P | ||||

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

| P |

| P |

| P |

| P |

| P |

| P |

| P |

| P | |

Register Bank 3

Address |

| Name |

| Reset Type |

| Bit 7 |

| Bit 6 |

| Bit 5 |

| Bit 4 |

| Bit 3 |

| Bit 2 |

| Bit 1 |

| Bit 0 |

|

|

|

| Bit Name |

| SMP |

| DCOL |

| BRS2 |

| BRS1 |

| BRS0 |

| EDS |

| DORD |

| WBE |

0x05 |

| SPIC1 |

|

| 0 |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 | |

| /RESET and WDT time out |

| P |

| P |

| P |

| P |

| P |

| P |

| P |

| 0 | |||

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

| P |

| P |

| P |

| P |

| P |

| P |

| P |

| P | |

|

|

|

| Bit Name |

| SPIS |

| X |

| X |

| X |

| X |

| SPIM1 |

| SPIM0 |

| RBF |

0x06 |

| SPIC2 |

|

| 0 |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 | |

| /RESET and WDT time out |

| 0 |

| 0 |

| 0 |

| 0 |

| 0 |

| P |

| P |

| 0 | |||

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

| 0 |

| P |

| P |

| P |

| P |

| P |

| P |

| P | |

|

|

|

| Bit Name |

| SPID17 |

| SPID16 |

| SPID15 |

| SPID14 |

| SPID13 |

| SPID12 |

| SPID11 |

| SPID10 |

0x07 |

| SPID1 |

|

| U |

| U |

| U |

| U |

| U |

| U |

| U |

| U | |

| /RESET and WDT time out |

| P |

| P |

| P |

| P |

| P |

| P |

| P |

| P | |||

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

| P |

| P |

| P |

| P |

| P |

| P |

| P |

| P | |

|

|

|

| Bit Name |

| X |

| X |

| /PHE81 |

| /PHE80 |

| /PHE63 |

| /PHE62 |

| /PHE61 |

| /PHE60 |

0x0A |

| PHC1 |

|

| U |

| U |

| 1 |

| 1 |

| 1 |

| 1 |

| 1 |

| 1 | |

| /RESET and WDT time out |

| U |

| U |

| 1 |

| 1 |

| 1 |

| 1 |

| 1 |

| 1 | |||

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

| U |

| U |

| P |

| P |

| P |

| P |

| P |

| P | |

|

|

|

| Bit Name |

| X |

| X |

| /PLE81 |

| /PLE80 |

| /PLE63 |

| /PLE62 |

| /PLE61 |

| /PLE60 |

0x0B |

| PLC2 |

|

| U |

| U |

| 1 |

| 1 |

| 1 |

| 1 |

| 1 |

| 1 | |

| /RESET and WDT time out |

| U |

| U |

| 1 |

| 1 |

| 1 |

| 1 |

| 1 |

| 1 | |||

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

| U |

| U |

| P |

| P |

| P |

| P |

| P |

| P | |

|

|

|

| Bit Name |

| X |

| X |

| X |

| X |

| /PHE73 |

| /PHE72 |

| /PHE71 |

| /PHE70 |

0x0C |

| PHC2 |

|

| U |

| U |

| U |

| U |

| 1 |

| 1 |

| 1 |

| 1 | |

| /RESET and WDT time out |

| U |

| U |

| U |

| U |

| 1 |

| 1 |

| 1 |

| 1 | |||

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

| U |

| U |

| U |

| U |

| P |

| P |

| P |

| P | |

|

|

|

| Bit Name |

| X |

| X |

| X |

| X |

| /PLE73 |

| /PLE72 |

| /PLE71 |

| /PLE70 |

0x0D |

| PLC2 |

|

| U |

| U |

| U |

| U |

| 1 |

| 1 |

| 1 |

| 1 | |

| /RESET and WDT time out |

| U |

| U |

| U |

| U |

| 1 |

| 1 |

| 1 |

| 1 | |||

|

|

|

|

|

|

|

|

|

|

|

| |||||||||

|

|

|

|

| U |

| U |

| U |

| U |

| P |

| P |

| P |

| P |

Product Specification (V1.0) 10.03.2006 | • 47 |

(This specification is subject to change without further notice)