January/April/October

Toolcat Mkttools GET AS4ADV36 Package

Table of Contents

Performance Observations and Tips

107

117

System Application Server Instance 119

10.2 DB2 for i5/OS access with Odbc 155

157

158

11.1

Supported Backup Device Rates 243

196

199

200

IPL Performance

17.7 File Level Backup Performance 292

19.6 User Pool Faulting Guidelines 310 19.7

284

285

Switchable IASP’s 327 Geographic Mirroring 329

334

335

What the Estimator is Not 335

Special Notices

Disclaimer Notice

Ipds

Purpose of this Document

Introduction

Page

Interactive Indicators and Metrics

ISeries and AS/400 Risc Server Model Performance Behavior

Overview

Disclaimer and Remaining Sections

3 V5R3

Server Model Behavior V4R5 V5R2

4 V5R2 and V5R1

Page

100

Server Model Differences

Custom Server Model

Model 7xx and 9/98 Model

Performance Highlights of Model 7xx Servers

Performance Highlights of Model 170 Servers

Performance Highlights of Custom Server Models

Additional Server Considerations

Interactive Utilization

Example

Server Dynamic Tuning SDT

Page

Affects of Server Dynamic Tuning

Interactive/Server characteristics in the real world

Managing Interactive Capacity

Is Interactive really Interactive?

Page

Migration from Traditional Models

Interval end time hour and minute

Number of interactive transactions per hour

Upgrade Considerations for Interactive Capacity

13.2 V5R1 DSD Performance Behavior

Domino-Complementary Processing

V5R1 Non-Domino Processing

Interactive Processing

Logical Partitioning on a Dedicated Server

Running Linux on a Dedicated Server

Page

Batch Performance

Effect of CPU Speed on Batch

Effect of Dasd Type on Batch

Batch Workload Description

Tuning Parameters for Batch

Expert Cache

Job Priority

Dynamic Priority Scheduling

Page

DB2 for i5/OS Performance

New for i5/OS V6R1

I5/OS V6R1 SQE Query Coverage

Query Attribute POWER5 Processor POWER6 Processor

DB2 i5/OS V5R4 Highlights

Records Inserted/Selected

I5/OS V5R4 SQE Query Coverage

I5/OS V5R3 Highlights

I5/OS V5R3 SQE Query Coverage

Common table expressions Deletes Derived tables

Like/Substring predicates DB2 Multisystem LOB columns

I5/OS V5R3 SQE Performance Enhancements

Partitioned Table Support

V5R2 Highlights Introduction of the SQL Query Engine

Materialized Query Table Support Fast Delete Support

SQE Optimizer

SQE Query Engine

SQE Database Statistics

Statistic Usage Example

Indexing

SQE for V5R2 Summary

Encoded Vector Indices EVIs

DB2 Symmetric Multiprocessing feature Introduction

DB2 for i5/OS Memory Sharing Considerations

Decision Support Queries

SMP Performance Summary

Journaling and Commitment Control

Journaling

Remote Journal Function

System-Managed Access Path Protection Smapp

Smapp

DB2 Multisystem for i5/OS

Commitment Control

Copyright IBM Corp

Referential Integrity

Triggers

Variable Length Fields

Description

Performance Expectations

Reuse Deleted Record Space

Description of Function

Comparison to Normal Inserts

Performance References for DB2

Copyright IBM Corp

Communications Performance

System i Ethernet Solutions

CCIN3

Communication Performance Test Environment

Hardware

Software

Communication and Storage observations

Dasd Performance

Large data transfer FTP

TCP/IP non-secure performance

Streaming Performance

RR & Acrr Performance

TCP/IP Secure Performance

SSL Performance

1167 565.4 530.0 479.6 462.1 202.2

249.7 53.4 48.0 31.3 27.4

478.4 55.7 53.3 36.9 31.9

SSL Relative Performance

VPN Performance

VPN Relative Performance

Performance Observations and Tips

27.5

10.9 15.4 18.7 88.8

Page

APPC, ICF, CPI-C, and Anynet

Page

HPR and Enterprise extender considerations

Test Type Hprip Link Hprip Link Speed AnyNet

Speed = 10Mbps = 100Mbps

Additional Information

For network information select Networking

Web Server and WebSphere Performance

Http Server powered by Apache

Relative Performance Metrics

Http Server powered by Apache for i5/OS

V5R4 Relative Capacity for CGI

Http Server powered by Apache for i5/OS

Page

Page

Page

Page

System Configuration

PHP Zend Core for

Zend Core for

Database and Workload Description

Database Access

OS / DB

Database Persistent versus Non-Persistent Connections

Database Isolation Levels

Zend Platform

PHP System Sizing

WebSphere Application Server

What’s new in V6R1?

Thi

Sho

Tuning changes in V6R1

Using direct map native Jdbc

Using ‘threadUsed=false custom property toolbox Jdbc

Use of unix sockets toolbox Jdbc

Page

Topology of the Trade Application

Page

WebSphere Application Server

Trade3 Measurement Results

Trade Capacity Results

Trade Scalability Results

Trade 6 Primitives

Description of Trade primitives in Figure

WebSphere Trade 3 Primitives

Accelerator for System

Trade Jdbc Response Time 1 User Time seconds

Page

WebSphere Application Server V51 Express

IBM WebFacing

WebFaced applications, one simple, one

Moderate, and one complex. See .4, for

Version 5.0 of Webfacing

More in line with the other two machines

Many 5250 applications have been implemented

With best performance techniques, such as

Tuning the Record Definition Cache

Display File Record I/O Processing

Cache Management Definition Cache Content Viewer

Cache Size Effect

Definitions would be retained in the cache with few cache

Misses for not commonly used records

Cache Viewer Button operations

Button Operation

Cache Management Record Definition Loader

Record Definition Loader Button operations Operation

Compression

Enabling Compression in IBM Http Server powered by Apache

Webfacing Compression

Additional Resources

PartnerWorld for Developers Webfacing website

WebSphere Host Access Transformation Services Hats

What’s new with V5R4 and Hats

Hats Customization

Hats Customization CPW/User

System Application Server Instance

IBM Systems Workload Estimator for Hats

Page

WebSphere Portal

WebSphere Commerce

Connect for iSeries

WebSphere Commerce Payments Performance Tips and Techniques

Connect for iSeries Connector Types

Performance Observations/Tips

Page

Java Performance

Introduction

What’s new in V6R1

IBM Technology for Java 32-bit and 64-bit

Native Code

Garbage Collection

Classic VM 64-bit

JIT Compiler

Page

Garbage Collection

Bytecode Verification

Determining Which JVM to Use

Functional Considerations

Performance Considerations

Capacity Planning

General Guidelines

Java Performance Tips and Techniques

I5/OS Specific Java Tips and Techniques

Classic VM-specific Tips

Consider the special property os400.jit.mmi.threshold

Java Language Performance Tips

Minimize synchronized methods

Instead, the above procedure should be written as

Java i5/OS Database Access Tips

Pool Database Connections

Resources

System i Cryptographic Solutions

IBM Software Solutions

IBM Hardware Solutions

Cryptography Performance

Cryptography Performance Test Environment

CSP API Sets

Software Cryptographic API Performance

Measurement Results

Hardware Cryptographic API Performance

Bytes/Second

Cipher Encrypt Performance

Encryption Threads

4764

Transactions/second Bytes/second

Cryptography Observations, Tips and Recommendations

CCA CSP

Supported number of 4764 Cryptographic Coprocessors

ISeries NetServer File Serving Performance

ISeries NetServer File Serving Performance

Response Time

Conclusion/Explanations

Page

10.1 DB2 for i5/OS access with Jdbc

Jdbc Performance Tuning Tips

DB2 for i5/OS Jdbc and Odbc Performance

References for Jdbc 10.2 DB2 for i5/OS access with Odbc

Odbc Performance Settings

Page

References for Odbc

Microsoft Odbc webpage

Domino on

Domino Workload Descriptions

Mail and Calendaring Users MCU

Domino Web Access formerly known as iNotes Web Access

Domino

Domino Domain Monitor

Domino Web Access client improvements with Domino

Additional memory was added for this test

Response Time and Megahertz relationship

Collaboration Edition and Domino Edition offerings

Collaboration Edition

Domino Edition

Performance Tips / Techniques

Page

Page

Domino Web Access

Domino Subsystem Tuning

Performance Monitoring Statistics

Main Storage Options

Minimize

Thousands

Sizing Domino on System

V5R3 Main Storage Options Response Times

Lpar and Partial Processor Considerations

Performance Data Collection Tools

System i NotesBench Audits and Benchmarks

WebSphere MQ for iSeries

Performance Improvements for WebSphere MQ V5.3 CSD6

Queue Manager Start Following an Abnormal End

Checkpoint Following a Journal Receiver Roll-over

Test Description and Results

Conclusions, Recommendations and Tips

Other Sources of Information

Basic Requirements -- Where Linux Runs

Linux on iSeries Performance

Summary

Key Ideas

Linux on iSeries Technical Overview

Linux on iSeries Architecture

Linux on iSeries Run-time Support

Basic Configuration and Performance Questions

General Performance Information and Results

Computational Performance -- C-based code

Number Processors Partition

Computational Performance -- Java

Web Serving Performance

TCP/IP Function Megabit Ethernet LAN Virtual LAN

Network Operations

Gcc and High Optimization gcc compiler option -O3

Gcc Compiler, Version

Value of Virtual LAN and Virtual Disk

Virtual Disk

13.7 DB2 UDB for Linux on iSeries

Linux on iSeries and IBM eServer Workload Estimator

Top Tips for Linux on iSeries Performance

Page

Page

Page

Dasd Performance

Internal Native Attachment

Direct Attach Native Hardware Characteristics

Devices & Controllers

14.1.2 iV5R2 Direct Attach Dasd

Intensive Workload Performance Comparison

Intensive Workload

14.1.3 571B

14.1.3.1 571B RAID5 vs RAID6 10 15K 35GB Dasd

14.1.3.2 571B IOP vs Iopless 10 15K 35GB Dasd

14.1.4 571B, 5709, 573D, 5703, 2780 IOA Comparison Chart

Dasd

14.1.4.4

14.1.5.1

Comparing 571E/574F and 571F/575B IOP and IOPLess

14.1.6.2

1000 2000 3000 4000 Ops/Sec

14.1.7.4

Performance Limits on the 571F/575B

14.1.8.1

Page

14.1.9.2 14.1.9.1

Direct Attach 571E/574F and 571F/575B Observations

New in iV5R4M5 14.2.1 9406-MMA CEC vs 9406-570 CEC Dasd

100 200 300 400 500 600 Ops/Sec

RAID Hot Spare

14.2.3 12X Loop Testing

New in iV6R1M0 Encrypted ASP

Non Encrypted ASP vs Encrypted ASP

Non Encrypted ASP vs Encrypted ASP

14.3.2 57B8/57B7 IOA

100 350 600 850 1100 1350 1600 1850

POWER6 520 57B8/57B7 6 RAID5 Dasd in CEC

14.3.3 572A IOA

Page

SAN Storage Area Network External

14.5 iV6R1M0 -- Vios and IVM Considerations

General Vios Considerations

Generic Concepts

Generic Configuration Concepts

Page

Page

Chdev -dev hdisk03 -attr pv=yes will assign a Pvid to hdisk3

Page

Vios and JS12 Express and JS22 Express Considerations

001 10000 20000 30000 40000 50000 60000

Vios

CPU Vios

Average Dasd Response Time Seconds

BladeCenter S and JS12 Express

Page

Page

System Workload Response Time Seconds

IBM i operating system 5.4 Virtual Scsi Performance

Page

Introduction

Virtual Scsi Performance Examples

Native vs. Virtual Performance

Virtual Scsi Bandwidth-Multiple Network Storage Spaces

Nwsd Read Scaling

Virtual Scsi Bandwidth-Disk Scaling

Sizing when using Dedicated Processors

Sizing

CPU milliseconds to process virtual Scsi I/O transaction

Sizing when using Micro-Partitioning

Sizing memory

Disk 1GB Sequential Read

AIX Virtual IO Client Performance Guide

Save/Restore Performance

Supported Backup Device Rates

Save Command Parameters that Affect Performance

Use Optimum Block Size Useoptblk

Data Compression Dtacpr

Data Compaction Compact

Workloads

Database File related Workloads

User Mix

User Mix 3GB contains 12,300 objects

Comparing Performance Data

Lower Performing Backup Devices

Medium & High Performing Backup Devices

Ultra High Performing Backup Devices

Use of Multiple Backup Devices

Parallel and Concurrent Library Measurements

Save and Restore Rates

Large File Concurrent

Save and Restore Rates

Large File Parallel

User Mix Concurrent Runs

User Mix Concurrent

450 440 430 420

Number of Processors Affect Performance

Dasd and Backup Devices Sharing a Tower

100

200

Virtual Tape

Data To Save Hours

500

Parallel Virtual Tapes

1500 1000

Concurrent Virtual Tapes

Save and Restore Scaling using a Virtual Tape Drive

Large File Virtual Tape Scaling Save Write to Virtual tape

Large File Save

User Mix Saves

High-End Tape Placement on System

PCI-X ™ In a 5094/5294 tower use slot C08 or C09

700

250

15.19 5XX Tape Device Rates

SLR60

Measurements in GB/HR all 8 Dasd in the system ASP

Source File 1GB

15.21 5XX DVD RAM and Optical Library

Software Compression

High

15.23 9406-MMA DVD RAM

ASP

15.24 9406-MMA 576B IOPLess IOA

1GB

What’s New and Tips on Performance What’s New IV6R1M0 March

IV5R4M5 July

IV5R4 January

August

IPL Performance

IPL Performance Considerations

IPL Test Description

Software Configuration

16.3 9406-MMA System Hardware Information

Active Database

1 iV5R4M5 Normal IPL Power-On Cold Start

16.4 9406-MMA IPL Performance Measurements Normal

16.5 9406-MMA IPL Performance Measurements Abnormal

1 iV5R4M5 Abnormal IPL Partition MSD

MSD Affects on IPL Performance Measurements

16.7.1 5XX Small system Hardware Configuration

16.7.2 5XX Large system Hardware Configuration

16.7 5XX System Hardware Information

Database

1 Normal IPL Power-On Cold Start

16.8 5XX IPL Performance Measurements Normal

16.9 5XX IPL Performance Measurements Abnormal

Measurement units are in hours, minutes and seconds

16.10 5XX IOP vs IOPLess effects on IPL Performance Normal

IPL Tips

Integrated BladeCenter and System x Performance

V5R4 iSCSI Host Bus Adapter iSCSI HBA

Integrated xSeries Adapter IXA

Effects of Windows and Linux loads on the host system

Integrated xSeries Servers IXS

17.2.1 IXS/IXA Disk I/O Operations

Extended Write Operations

ISCSI Disk I/O Operations

ISCSI virtual I/O private memory pool

Crtsbsd SBSDQGPL/QFPHIS POOLS1 10000

Virtual Ethernet Connections

17.2.5 IXS/IXA IOP Resource

IXS and IXA attached servers

ISCSI attached servers

Disk I/O CPU Cost

Machine Pool MBytes Base Pool Qfphis Private Pool Total

Further notes about IXS/IXA Disk Operations

CPW per 1k Disk Operations

Disk I/O Throughput

ISCSI Target, IXA Capacity Comparison MB per Second

Virtual Ethernet CPU Cost and Capacities

VE Capacity Comparisons

VE CPW Cost

PP TCP Stream i5/OS to Windows

File Level Backup Performance

Windows CPU Cost

Additional Sources of Information

Flbu SAV / RST Rates

Microsoft Hardware Compatibility Test URL See

Logical Partitioning Lpar

V5R3 Information

V5R2 Additions

General Tips

Considerations

V5R1 Additions

Lpar Performance Considerations

Performance on a 12-way system

Page

Lpar Throughput Increase

Lpar Measurements

Over a Standalone 12-way

5920 26 %

5700 21 %

Miscellaneous Performance Information

TPC-C Commercial Performance

SAP Performance Information

SPECjbb2000

VolanoMark

Delay Cost Terminology

Dynamic Priority Scheduling

Priority Mapping to Delay Cost Curves

Performance Testing Results

Qdynptyscd = ‘1’ on Qdynptyscd = ‘0’

Memory Tuning Using the Qpfradj System Value

Main Storage Sizing Guidelines

Additional Memory Tuning Techniques

User Pool Faulting Guidelines

Setobjacc Set Object Access

Large Memory Systems

Interactive

Batch

19.7 AS/400 NetFinity Capacity Planning

AS/400 NetFinity Software Inventory Performance

Conclusions/Recommendations for NetFinity

Adjusting Your Performance Tuning for Threads

General Performance Tips and Techniques

History

Coming Change

Problem

Solution

General Performance Guidelines -- Effects of Compilation

In-lining

Optimization Levels

Theory -- and Practice

System Level Considerations

Typical Storage Costs

Order1 Orderj Ordert OrderN

Brief Example

Which is more important?

Short but Important Tip about Data Base

Final Thought About Memory and Competitiveness

Hardware Multi-threading HMT

HMT Described

HMT Feature SMT Feature

HMT and SMT Compared and Contrasted

Some key similarities and differences are

Models With/Without HMT

POWER6 520 Memory Considerations

Aligning Floating Point Data on Power6

Page

High Availability Switchable Resources Considerations

Switchable IASP’s

High Availability Performance

Workload Description

Workload Configuration

System Configuration

Hardware Configuration

Cabling Map

Switchover Tips

Geographic Mirroring

Workload Description

Large System Configuration

Hardware Configuration Cabling Map

Switchable Towers using Geographic Mirroring

Geographic Mirroring Measurements

Synchronization on an idle system

Active State

Geographic Mirroring Tips

IBM Systems Workload Estimator

Estimator Access

Merging PM for System i data into the Estimator

What the Estimator is Not

Page

Appendix A. CPW and CIW Descriptions

Commercial Processing Workload CPW

CPW Application Description

Compute Intensive Workload CIW

Page

Page

Performance Data Collection Services

How Collection Services works

Starting Collection Services

Batch Modeling Tool Bchmdl

Page

Page

CPW values for the IBM Power Systems IBM i operating system

V6R1 Additions October

CPW values for the IBM Power 595 IBM i operating system

V6R1 Additions August

V6R1 Additions April

Table C.3.1. CPW values for Power System Models

V6R1 Additions January

IBM System i using the POWER6 processor technology

IBM System i using the POWER5 processor technology

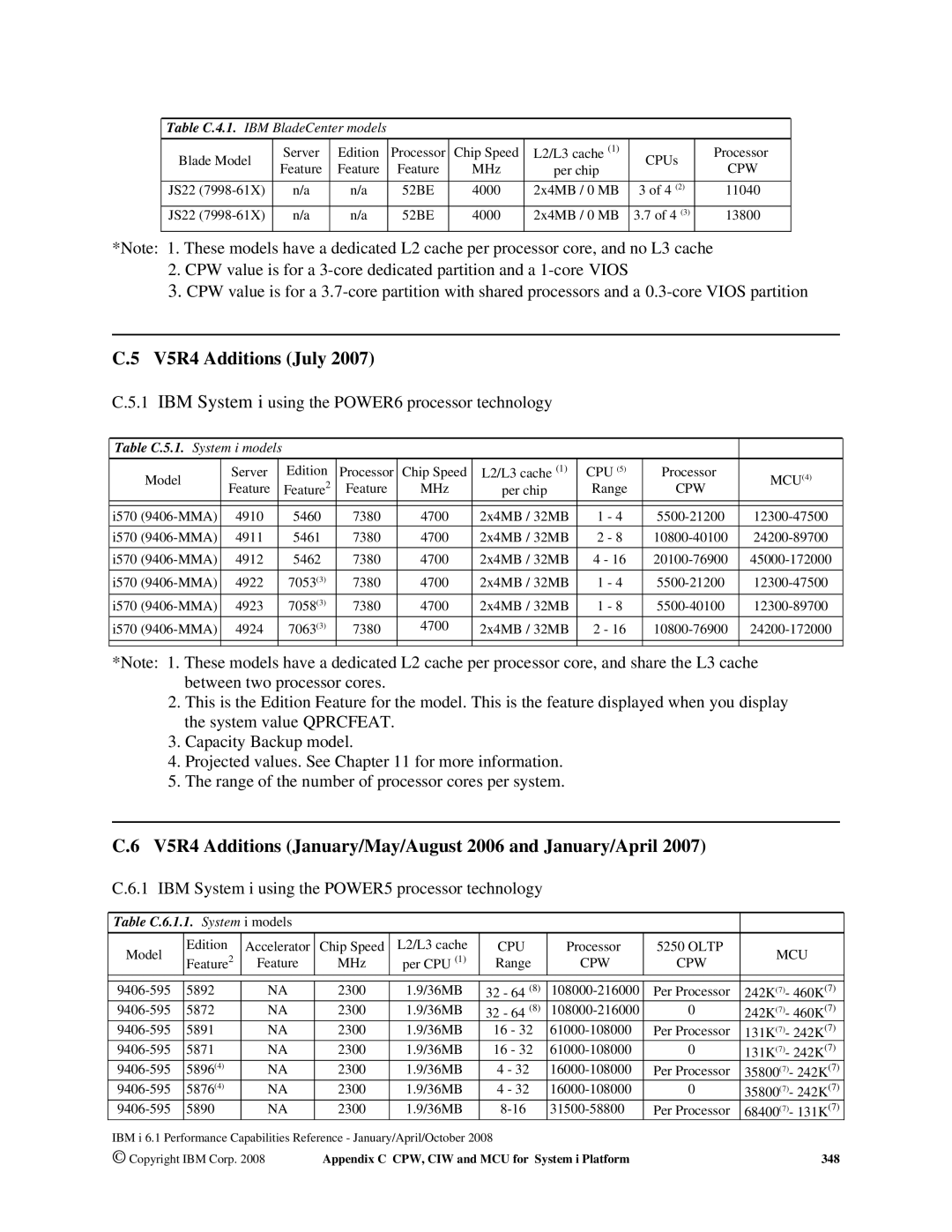

V5R4 Additions July

V5R4 Additions January/May/August 2006 and January/April

Model Edition Accelerator

V5R3 Additions May, July, August, October 2004, July

IBM ~ i5 Servers

Value

Express

CPU

V5R2 Additions February, May, July

ISeries Model 8xx Servers

750

540

Model 810 and 825 iSeries for Domino February

V5R2 Additions

Models share L2 cache between 2 processors

Standard Models 8xx Servers

10 V5R1 Additions

Table C.9.2.1 Standard Models 8xx Servers

Model 8xx Servers

Table C.9.1.1 Model 8xx Servers

Model 2xx Servers

10.3 V5R1 Dedicated Server for Domino

Table C.10.2.1 Model 2xx Servers

Table C.10.3 .1 Dedicated Servers for Domino

Capacity Upgrade on-demand Models

CPW Values and Interactive Features for CUoD Models

Active Stand-by 840-2352 840-2353 840-2354

Table C.10.4.1.1 V5R1 Capacity Upgrade on-demand Models

16500

11 V4R5 Additions

11.1 AS/400e Model 8xx Servers

Table C.11.1 Model 8xx Servers All new Condor models

Dedicated Server for Domino

Table C.11.2.1 Model 2xx Servers

Table C.11.3.1 Dedicated Server for Domino

SB Models

12 V4R4 Additions

12.1 AS/400e Model 7xx Servers

Table C.11.4.1 SB Models

Model 170 Servers Current 170 Servers

Table C.12.2.1 Current Model 170 Servers

AS/400e Dedicated Server for Domino

Previous Model 170 Servers

2407 2408 2409 120

Table C.12.2.2 Dedicated Server for Domino

13 AS/400e Model Sxx Servers

14 AS/400e Custom Servers

15 AS/400 Advanced Servers

Table C.13.1 AS/400e Servers

16 AS/400e Custom Application Server Model SB1

Table C.15.1 AS/400 Advanced Servers V4R1 and V4R2

Table C.15.2 AS/400 Advanced Servers V3R7

17 AS/400 Models 4xx, 5xx and 6xx Systems

Table C.16.1 AS/400e Custom Application Server Model SB1

Table C.17.1 AS/400 Risc Systems

Table C.17.2 AS/400e Systems

18 AS/400 Cisc Model Capacities

Table C.18.6 AS/400 Cisc Model 9406 Systems

Table C.18.7 AS/400 Advanced Systems Cisc

Table C.18.8 AS/400 Advanced Servers Cisc