Networking Silicon — 82555

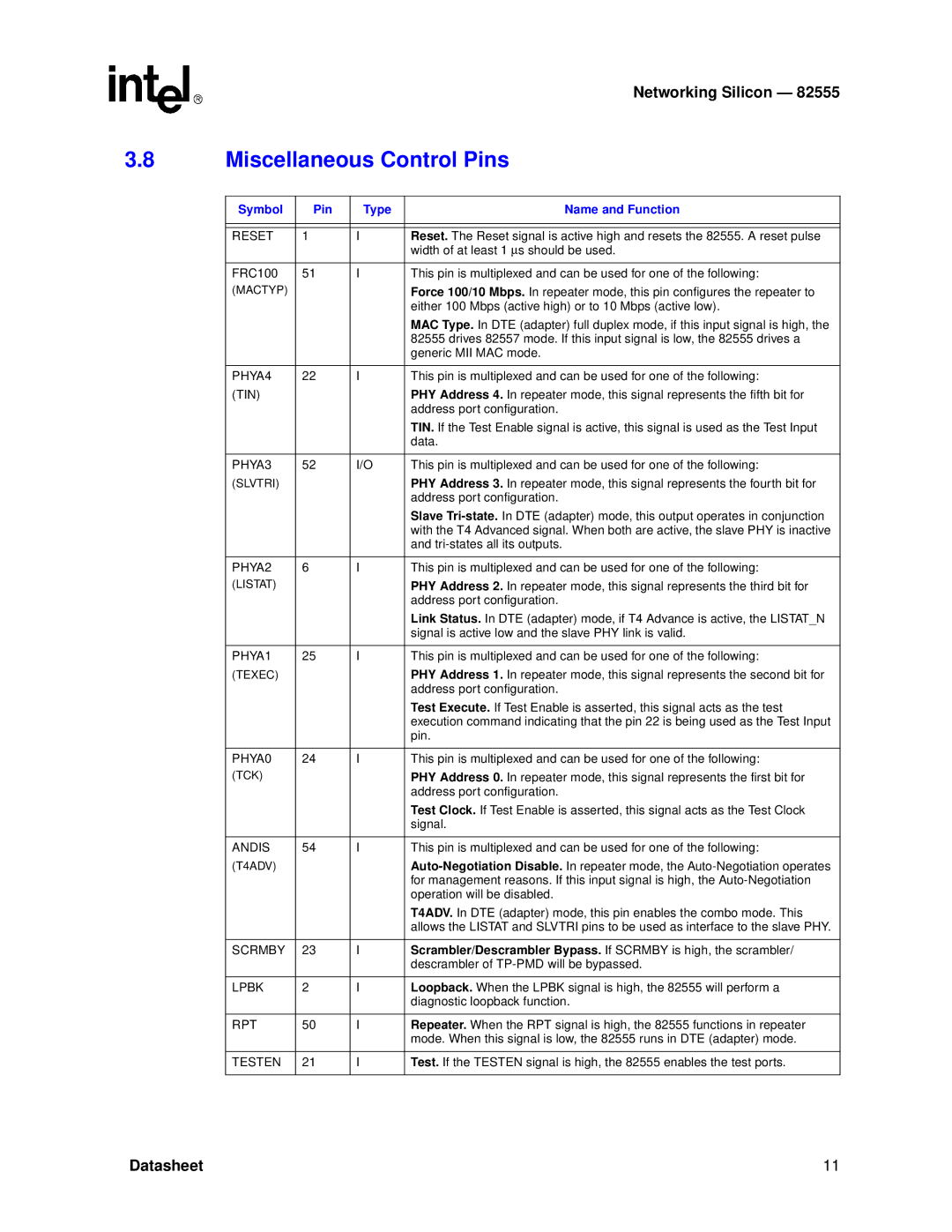

3.8Miscellaneous Control Pins

Symbol | Pin | Type | Name and Function |

|

|

|

|

|

|

|

|

RESET | 1 | I | Reset. The Reset signal is active high and resets the 82555. A reset pulse |

|

|

| width of at least 1 μs should be used. |

|

|

|

|

FRC100 | 51 | I | This pin is multiplexed and can be used for one of the following: |

(MACTYP) |

|

| Force 100/10 Mbps. In repeater mode, this pin configures the repeater to |

|

|

| either 100 Mbps (active high) or to 10 Mbps (active low). |

|

|

| MAC Type. In DTE (adapter) full duplex mode, if this input signal is high, the |

|

|

| 82555 drives 82557 mode. If this input signal is low, the 82555 drives a |

|

|

| generic MII MAC mode. |

|

|

|

|

PHYA4 | 22 | I | This pin is multiplexed and can be used for one of the following: |

(TIN) |

|

| PHY Address 4. In repeater mode, this signal represents the fifth bit for |

|

|

| address port configuration. |

|

|

| TIN. If the Test Enable signal is active, this signal is used as the Test Input |

|

|

| data. |

|

|

|

|

PHYA3 | 52 | I/O | This pin is multiplexed and can be used for one of the following: |

(SLVTRI) |

|

| PHY Address 3. In repeater mode, this signal represents the fourth bit for |

|

|

| address port configuration. |

|

|

| Slave |

|

|

| with the T4 Advanced signal. When both are active, the slave PHY is inactive |

|

|

| and |

|

|

|

|

PHYA2 | 6 | I | This pin is multiplexed and can be used for one of the following: |

(LISTAT) |

|

| PHY Address 2. In repeater mode, this signal represents the third bit for |

|

|

| address port configuration. |

|

|

| Link Status. In DTE (adapter) mode, if T4 Advance is active, the LISTAT_N |

|

|

| signal is active low and the slave PHY link is valid. |

|

|

|

|

PHYA1 | 25 | I | This pin is multiplexed and can be used for one of the following: |

(TEXEC) |

|

| PHY Address 1. In repeater mode, this signal represents the second bit for |

|

|

| address port configuration. |

|

|

| Test Execute. If Test Enable is asserted, this signal acts as the test |

|

|

| execution command indicating that the pin 22 is being used as the Test Input |

|

|

| pin. |

|

|

|

|

PHYA0 | 24 | I | This pin is multiplexed and can be used for one of the following: |

(TCK) |

|

| PHY Address 0. In repeater mode, this signal represents the first bit for |

|

|

| address port configuration. |

|

|

| Test Clock. If Test Enable is asserted, this signal acts as the Test Clock |

|

|

| signal. |

|

|

|

|

ANDIS | 54 | I | This pin is multiplexed and can be used for one of the following: |

(T4ADV) |

|

| |

|

|

| for management reasons. If this input signal is high, the |

|

|

| operation will be disabled. |

|

|

| T4ADV. In DTE (adapter) mode, this pin enables the combo mode. This |

|

|

| allows the LISTAT and SLVTRI pins to be used as interface to the slave PHY. |

|

|

|

|

SCRMBY | 23 | I | Scrambler/Descrambler Bypass. If SCRMBY is high, the scrambler/ |

|

|

| descrambler of |

|

|

|

|

LPBK | 2 | I | Loopback. When the LPBK signal is high, the 82555 will perform a |

|

|

| diagnostic loopback function. |

|

|

|

|

RPT | 50 | I | Repeater. When the RPT signal is high, the 82555 functions in repeater |

|

|

| mode. When this signal is low, the 82555 runs in DTE (adapter) mode. |

|

|

|

|

TESTEN | 21 | I | Test. If the TESTEN signal is high, the 82555 enables the test ports. |

|

|

|

|

Datasheet | 11 |