82555 — Networking Silicon

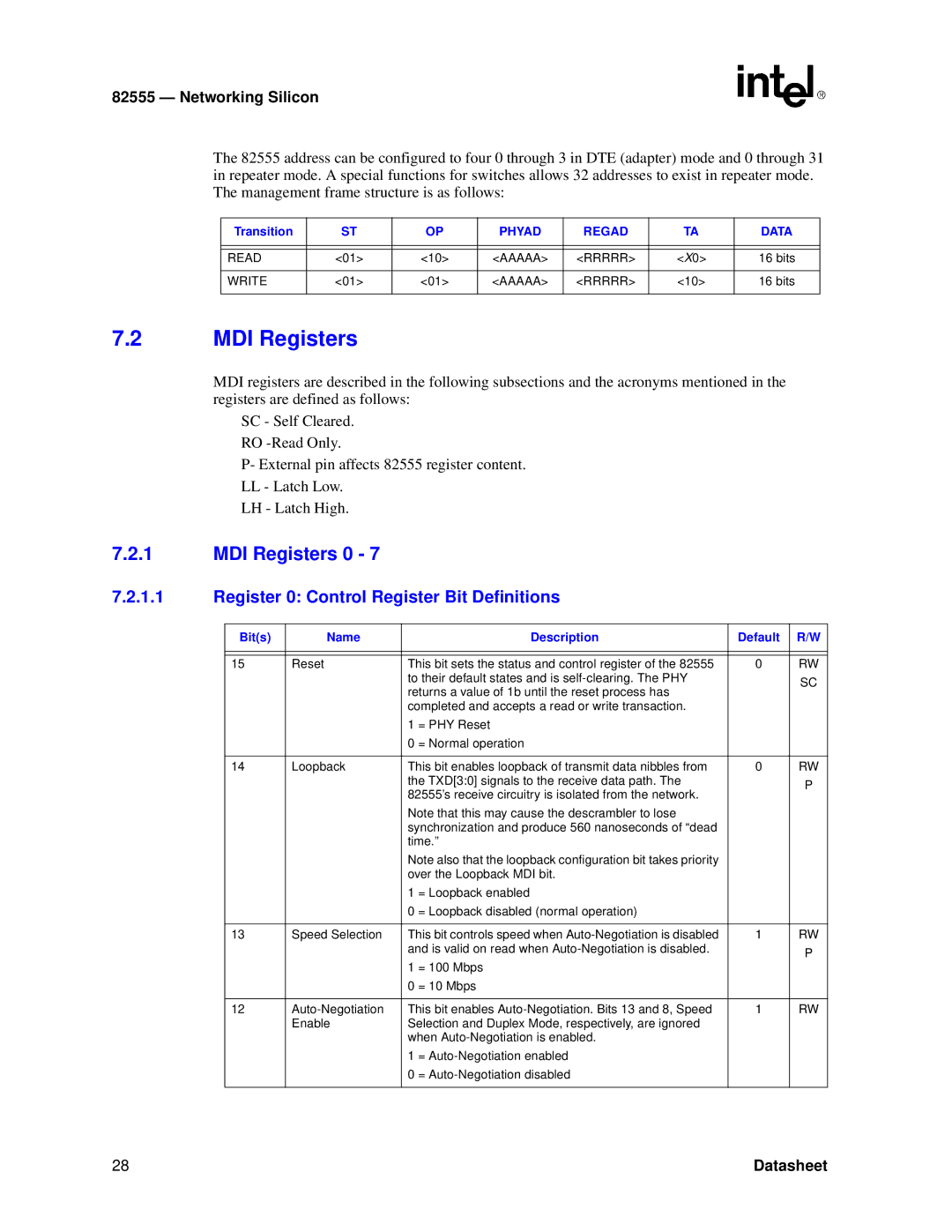

The 82555 address can be configured to four 0 through 3 in DTE (adapter) mode and 0 through 31 in repeater mode. A special functions for switches allows 32 addresses to exist in repeater mode. The management frame structure is as follows:

Transition | ST | OP | PHYAD | REGAD | TA | DATA |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

READ | <01> | <10> | <AAAAA> | <RRRRR> | <X0> | 16 bits |

|

|

|

|

|

|

|

WRITE | <01> | <01> | <AAAAA> | <RRRRR> | <10> | 16 bits |

|

|

|

|

|

|

|

7.2MDI Registers

MDI registers are described in the following subsections and the acronyms mentioned in the registers are defined as follows:

SC - Self Cleared.

RO

P- External pin affects 82555 register content.

LL- Latch Low. LH - Latch High.

7.2.1MDI Registers 0 - 7

7.2.1.1Register 0: Control Register Bit Definitions

Bit(s) | Name |

| Description | Default | R/W |

|

|

|

|

| |

|

|

|

|

| |

15 | Reset | This bit sets the status and control register of the 82555 | 0 | RW | |

|

| to their default states and is |

| SC | |

|

| returns a value of 1b until the reset process has |

| ||

|

|

|

| ||

|

| completed and accepts a read or write transaction. |

|

| |

|

| 1 | = PHY Reset |

|

|

|

| 0 | = Normal operation |

|

|

|

|

|

|

| |

14 | Loopback | This bit enables loopback of transmit data nibbles from | 0 | RW | |

|

| the TXD[3:0] signals to the receive data path. The |

| P | |

|

| 82555’s receive circuitry is isolated from the network. |

| ||

|

|

|

| ||

|

| Note that this may cause the descrambler to lose |

|

| |

|

| synchronization and produce 560 nanoseconds of “dead |

|

| |

|

| time.” |

|

| |

|

| Note also that the loopback configuration bit takes priority |

|

| |

|

| over the Loopback MDI bit. |

|

| |

|

| 1 | = Loopback enabled |

|

|

|

| 0 | = Loopback disabled (normal operation) |

|

|

|

|

|

|

| |

13 | Speed Selection | This bit controls speed when | 1 | RW | |

|

| and is valid on read when |

| P | |

|

|

|

|

| |

|

| 1 | = 100 Mbps |

|

|

|

| 0 | = 10 Mbps |

|

|

|

|

|

|

| |

12 | This bit enables | 1 | RW | ||

| Enable | Selection and Duplex Mode, respectively, are ignored |

|

| |

|

| when |

|

| |

|

| 1 | = |

|

|

|

| 0 | = |

|

|

|

|

|

|

|

|

28 | Datasheet |