82555 — Networking Silicon

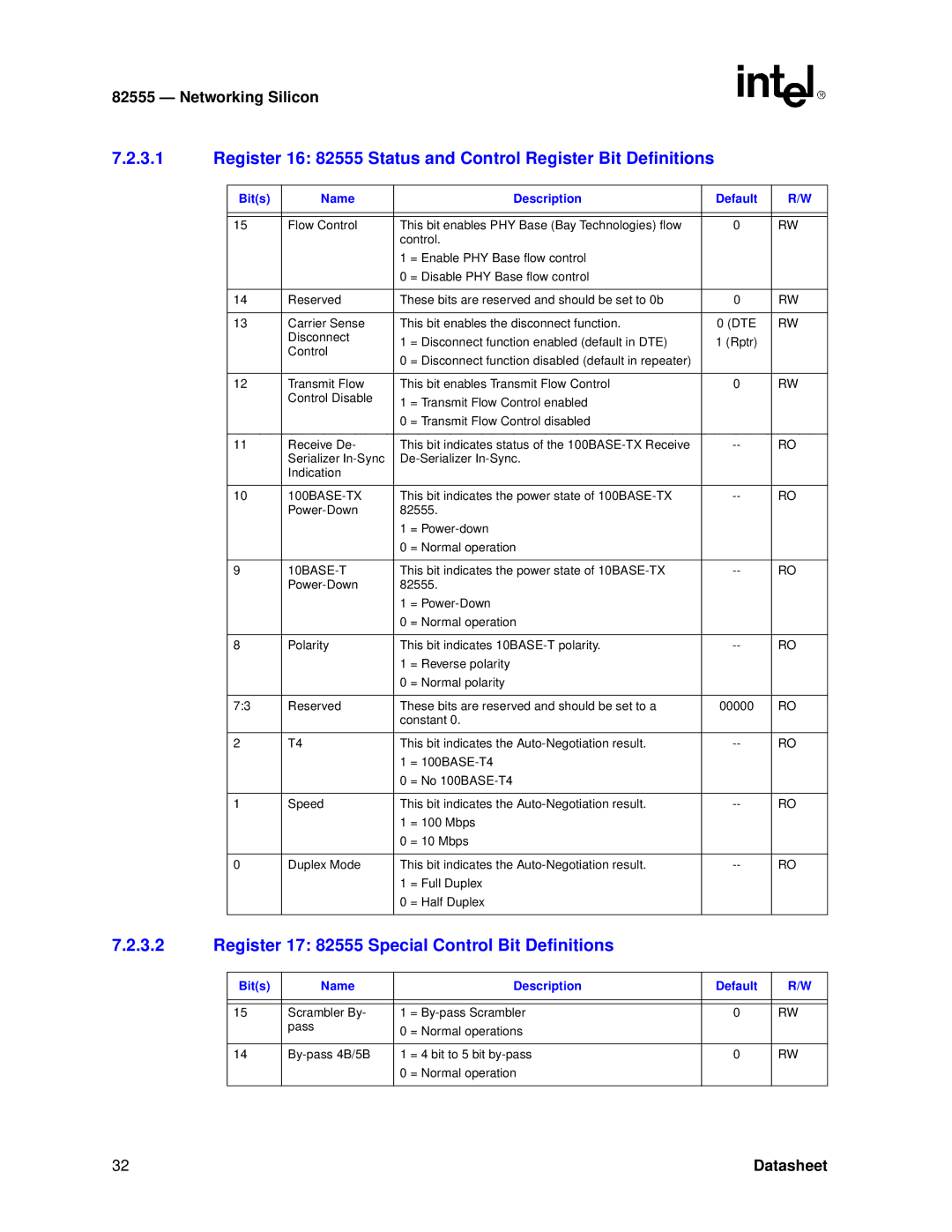

7.2.3.1Register 16: 82555 Status and Control Register Bit Definitions

Bit(s) | Name |

| Description | Default | R/W |

|

|

|

|

| |

|

|

|

|

| |

15 | Flow Control | This bit enables PHY Base (Bay Technologies) flow | 0 | RW | |

|

| control. |

|

| |

|

| 1 | = Enable PHY Base flow control |

|

|

|

| 0 | = Disable PHY Base flow control |

|

|

|

|

|

|

| |

14 | Reserved | These bits are reserved and should be set to 0b | 0 | RW | |

|

|

|

|

| |

13 | Carrier Sense | This bit enables the disconnect function. | 0 (DTE | RW | |

| Disconnect | 1 | = Disconnect function enabled (default in DTE) | 1 (Rptr) |

|

| Control |

| |||

| 0 | = Disconnect function disabled (default in repeater) |

|

| |

|

|

|

| ||

|

|

|

|

| |

12 | Transmit Flow | This bit enables Transmit Flow Control | 0 | RW | |

| Control Disable | 1 | = Transmit Flow Control enabled |

|

|

|

|

|

| ||

|

| 0 | = Transmit Flow Control disabled |

|

|

|

|

|

|

| |

11 | Receive De- | This bit indicates status of the | RO | ||

| Serializer |

|

| ||

| Indication |

|

|

|

|

|

|

|

|

| |

10 |

| This bit indicates the power state of | RO | ||

| 82555. |

|

| ||

|

| 1 | = |

|

|

|

| 0 | = Normal operation |

|

|

|

|

|

|

| |

9 |

| This bit indicates the power state of | RO | ||

| 82555. |

|

| ||

|

| 1 | = |

|

|

|

| 0 | = Normal operation |

|

|

|

|

|

|

| |

8 | Polarity | This bit indicates | RO | ||

|

| 1 | = Reverse polarity |

|

|

|

| 0 | = Normal polarity |

|

|

|

|

|

|

| |

7:3 | Reserved | These bits are reserved and should be set to a | 00000 | RO | |

|

| constant 0. |

|

| |

|

|

|

|

| |

2 | T4 | This bit indicates the | RO | ||

|

| 1 | = |

|

|

|

| 0 | = No |

|

|

|

|

|

|

| |

1 | Speed | This bit indicates the | RO | ||

|

| 1 | = 100 Mbps |

|

|

|

| 0 | = 10 Mbps |

|

|

|

|

|

|

| |

0 | Duplex Mode | This bit indicates the | RO | ||

|

| 1 | = Full Duplex |

|

|

|

| 0 | = Half Duplex |

|

|

|

|

|

|

|

|

7.2.3.2Register 17: 82555 Special Control Bit Definitions

Bit(s) | Name |

| Description | Default | R/W |

|

|

|

|

|

|

|

|

|

|

|

|

15 | Scrambler By- | 1 | = | 0 | RW |

| pass | 0 | = Normal operations |

|

|

|

|

|

| ||

|

|

|

|

| |

14 | 1 = 4 bit to 5 bit | 0 | RW | ||

|

| 0 | = Normal operation |

|

|

|

|

|

|

|

|

32 | Datasheet |