|

|

| Networking Silicon — 82555 |

|

|

|

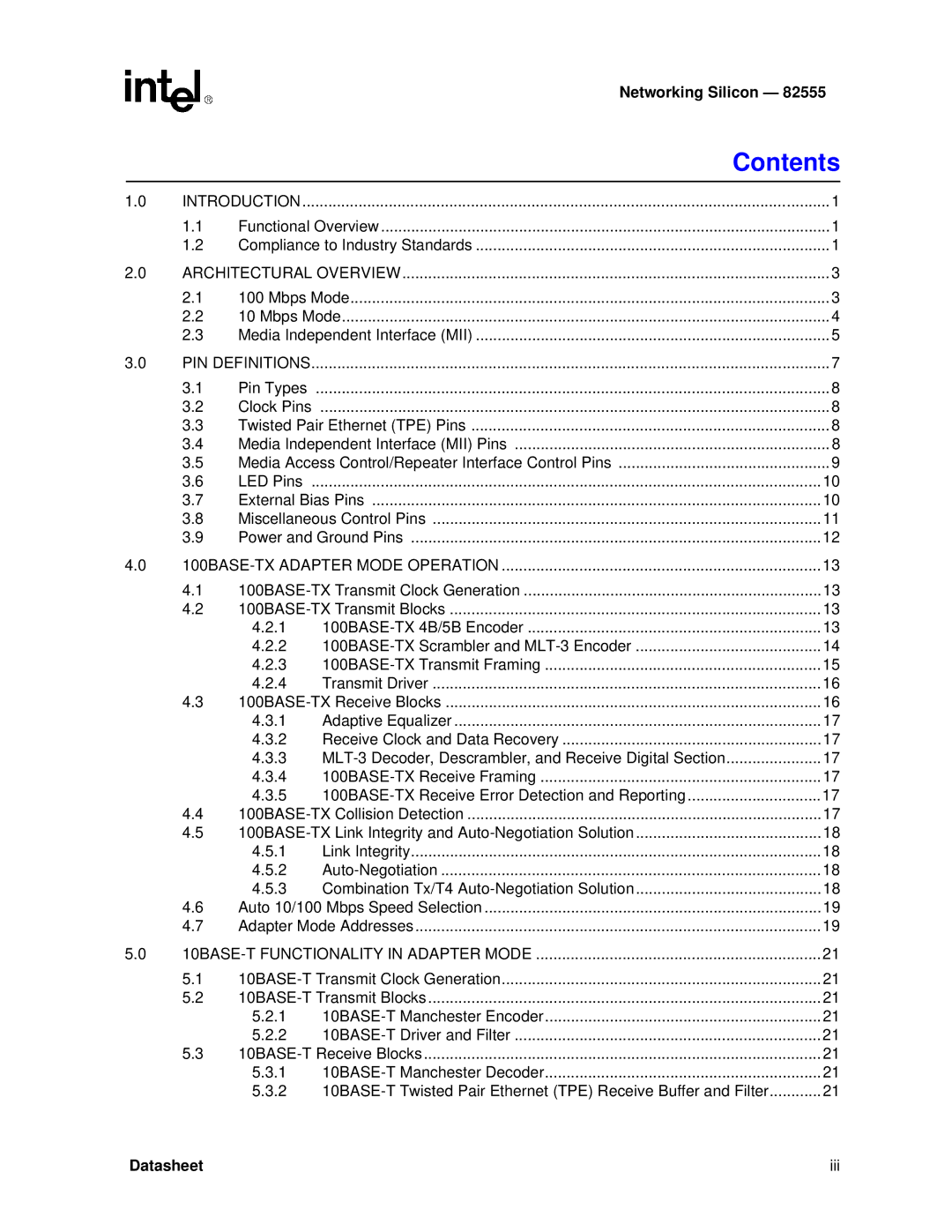

| Contents | |

|

|

|

| |

1.0 | INTRODUCTION | 1 | ||

| 1.1 | Functional Overview | 1 | |

| 1.2 | Compliance to Industry Standards | 1 | |

2.0 | ARCHITECTURAL OVERVIEW | 3 | ||

| 2.1 | 100 Mbps Mode | 3 | |

| 2.2 | 10 Mbps Mode | 4 | |

| 2.3 | Media Independent Interface (MII) | 5 | |

3.0 | PIN DEFINITIONS | 7 | ||

| 3.1 | Pin Types | 8 | |

| 3.2 | Clock Pins | 8 | |

| 3.3 | Twisted Pair Ethernet (TPE) Pins | 8 | |

| 3.4 | Media Independent Interface (MII) Pins | 8 | |

| 3.5 | Media Access Control/Repeater Interface Control Pins | 9 | |

| 3.6 | LED Pins | 10 | |

| 3.7 | External Bias Pins | 10 | |

| 3.8 | Miscellaneous Control Pins | 11 | |

| 3.9 | Power and Ground Pins | 12 | |

4.0 | 13 | |||

| 4.1 | 13 | ||

| 4.2 | 13 | ||

|

| 4.2.1 | 13 | |

|

| 4.2.2 | 14 | |

|

| 4.2.3 | 15 | |

|

| 4.2.4 | Transmit Driver | 16 |

| 4.3 | 16 | ||

|

| 4.3.1 | Adaptive Equalizer | 17 |

|

| 4.3.2 | Receive Clock and Data Recovery | 17 |

|

| 4.3.3 | 17 | |

|

| 4.3.4 | 17 | |

|

| 4.3.5 | 17 | |

| 4.4 | 17 | ||

| 4.5 | 18 | ||

|

| 4.5.1 | Link Integrity | 18 |

|

| 4.5.2 | 18 | |

|

| 4.5.3 | Combination Tx/T4 | 18 |

| 4.6 | Auto 10/100 Mbps Speed Selection | 19 | |

| 4.7 | Adapter Mode Addresses | 19 | |

5.0 | 21 | |||

| 5.1 | 21 | ||

| 5.2 | 21 | ||

|

| 5.2.1 | 21 | |

|

| 5.2.2 | 21 | |

| 5.3 | 21 | ||

|

| 5.3.1 | 21 | |

|

| 5.3.2 | 21 | |

Datasheet | iii |