82555 — Networking Silicon

1.5V |

|

T4,T5,T6 | T4,T5,T6 |

| T1,T2,T3 |

Figure 14. MII Clocks AC Timing

11.4.2MII Timing Parameters

| Symbol | Parameter | Conditions | Min | Typ | Max | Units |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T7 | TTXDV | TXD[3:0], TXEN, TXERR setup |

| 15 |

| 25 | ns |

from the rising edge of TXC |

|

| |||||

T8 | TTXH | TXD[3:0], TXEN, TXERR hold |

| 0 |

|

| ns |

time after the rising edge of TXC |

|

|

| ||||

T9 | TRXSU | RXD[3:0], RXDV, RXERR valid |

| 10 |

|

| ns |

before the rising edge of RXC |

|

|

| ||||

T10 | TRXH | RXD[3:0], RXDV, RXERR hold |

| 10 |

|

| ns |

time after the rising edge of RXC |

|

|

| ||||

T11 | TMSU | MDIO setup time to the rising | MDIO input | 10 |

|

| ns |

edge of MDC |

|

| |||||

T12 | TMH | MDIO hold time from the rising | MDIO input | 10 |

|

| ns |

edge of MDC |

|

| |||||

T13 | TMV | MDIO valid from the rising edge | MDIO output | 300 |

|

| ns |

of MDC |

|

|

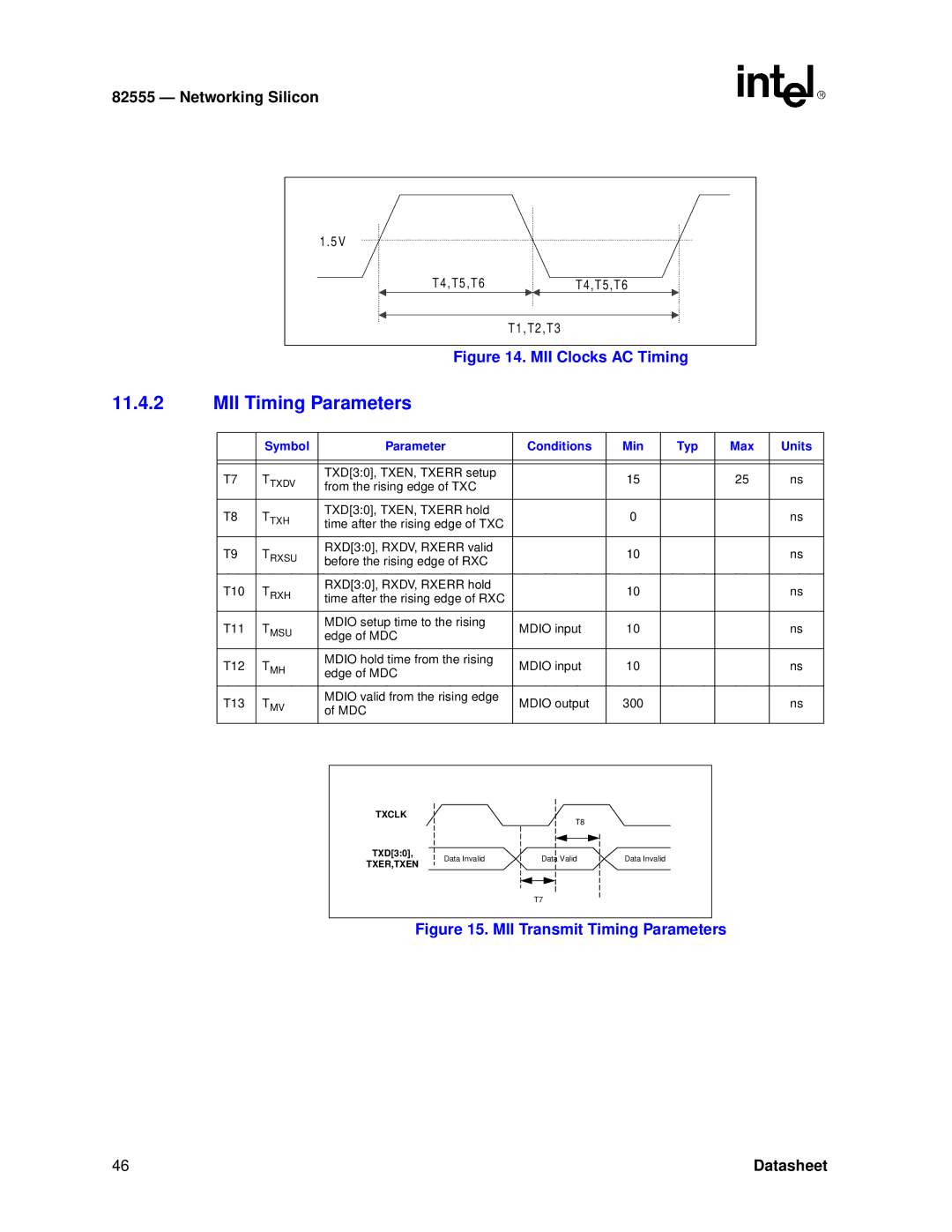

TXCLK

TXD[3:0],

TXER,TXEN

Data Invalid

T8

Data Valid

T7

Data Invalid

Figure 15. MII Transmit Timing Parameters

46 | Datasheet |