82555 — Networking Silicon

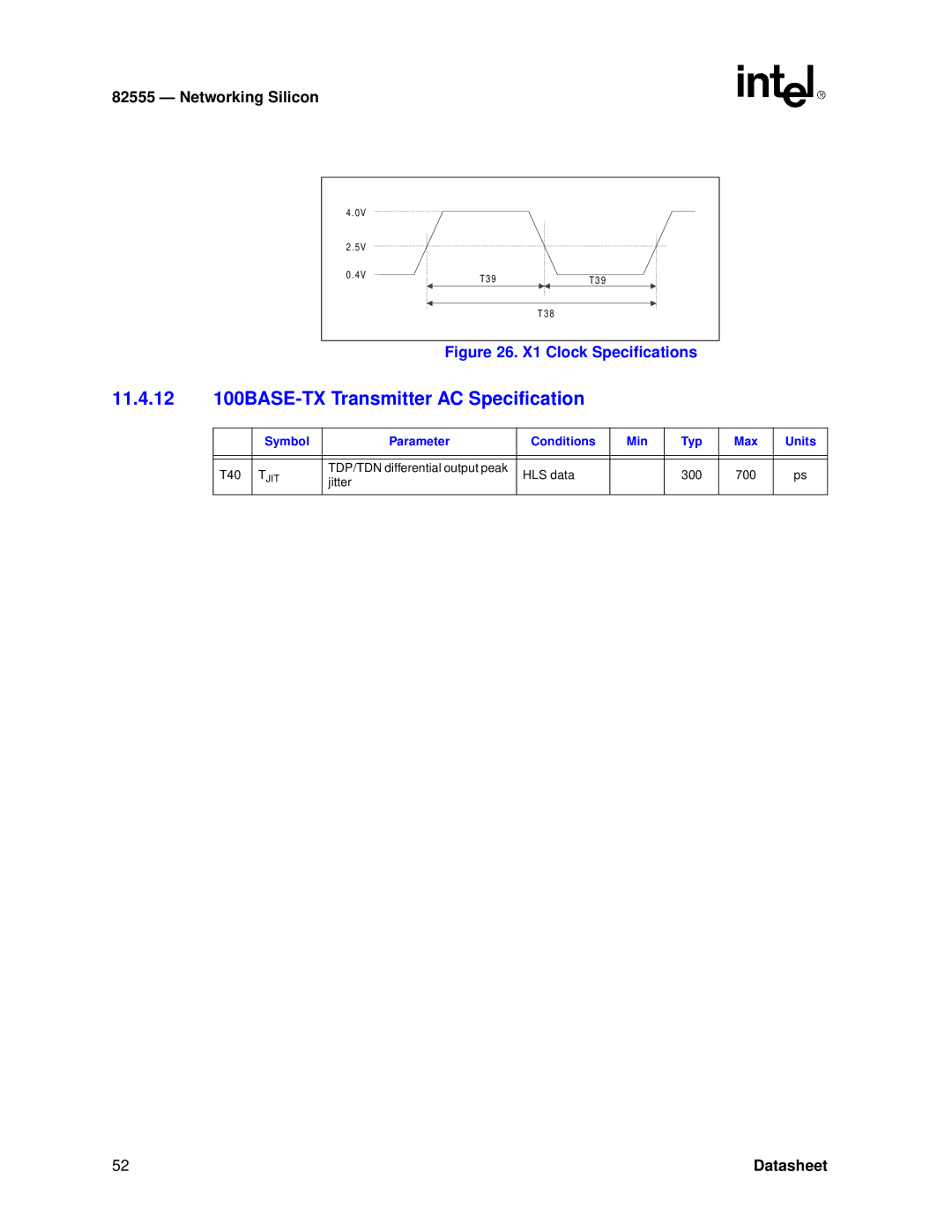

4.0V |

|

|

2.5V |

|

|

0.4V | T39 | T39 |

| ||

|

| T38 |

Figure 26. X1 Clock Specifications

11.4.12100BASE-TX Transmitter AC Specification

| Symbol | Parameter | Conditions | Min | Typ | Max | Units |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

T40 | TJIT | TDP/TDN differential output peak | HLS data |

| 300 | 700 | ps |

jitter |

|

52 | Datasheet |