82555 — Networking Silicon

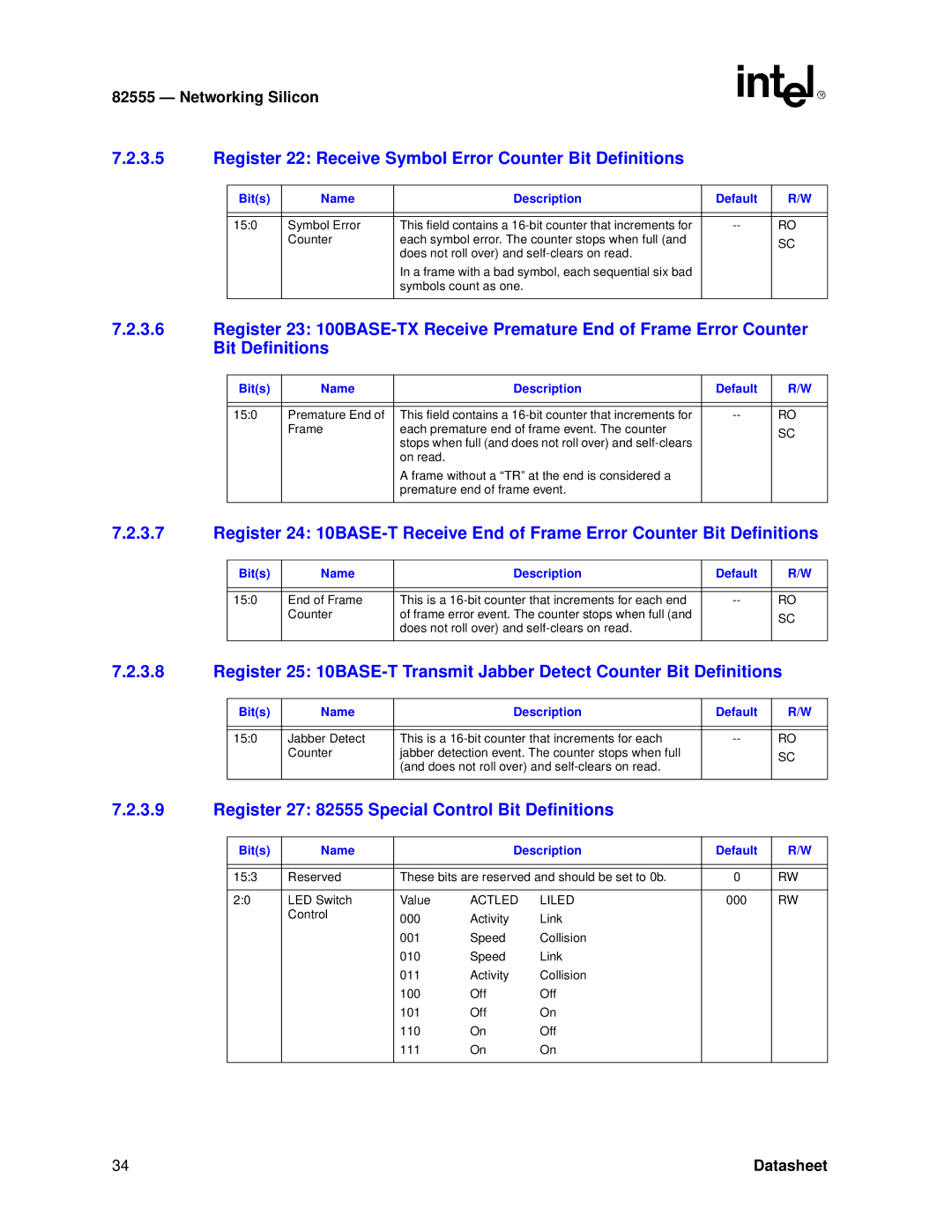

7.2.3.5Register 22: Receive Symbol Error Counter Bit Definitions

Bit(s) | Name | Description | Default | R/W |

|

|

|

|

|

|

|

|

|

|

15:0 | Symbol Error | This field contains a | RO | |

| Counter | each symbol error. The counter stops when full (and |

| SC |

|

| does not roll over) and |

| |

|

|

|

| |

|

| In a frame with a bad symbol, each sequential six bad |

|

|

|

| symbols count as one. |

|

|

|

|

|

|

|

7.2.3.6Register 23:

Bit(s) | Name | Description | Default | R/W |

|

|

|

|

|

|

|

|

|

|

15:0 | Premature End of | This field contains a | RO | |

| Frame | each premature end of frame event. The counter |

| SC |

|

| stops when full (and does not roll over) and |

| |

|

|

|

| |

|

| on read. |

|

|

|

| A frame without a “TR” at the end is considered a |

|

|

|

| premature end of frame event. |

|

|

|

|

|

|

|

7.2.3.7Register 24:

Bit(s) | Name | Description | Default | R/W |

|

|

|

|

|

|

|

|

|

|

15:0 | End of Frame | This is a | RO | |

| Counter | of frame error event. The counter stops when full (and |

| SC |

|

| does not roll over) and |

| |

|

|

|

| |

|

|

|

|

|

7.2.3.8Register 25:

Bit(s) | Name | Description | Default | R/W |

|

|

|

|

|

|

|

|

|

|

15:0 | Jabber Detect | This is a | RO | |

| Counter | jabber detection event. The counter stops when full |

| SC |

|

| (and does not roll over) and |

| |

|

|

|

| |

|

|

|

|

|

7.2.3.9Register 27: 82555 Special Control Bit Definitions

Bit(s) | Name |

| Description | Default | R/W | |

|

|

|

|

| ||

|

|

|

|

| ||

15:3 | Reserved | These bits are reserved and should be set to 0b. | 0 | RW | ||

|

|

|

|

|

|

|

2:0 | LED Switch | Value | ACTLED | LILED | 000 | RW |

| Control | 000 | Activity | Link |

|

|

|

|

|

| |||

|

| 001 | Speed | Collision |

|

|

|

| 010 | Speed | Link |

|

|

|

| 011 | Activity | Collision |

|

|

|

| 100 | Off | Off |

|

|

|

| 101 | Off | On |

|

|

|

| 110 | On | Off |

|

|

|

| 111 | On | On |

|

|

|

|

|

|

|

|

|

34 | Datasheet |