Networking Silicon — 82555

2.0Architectural Overview

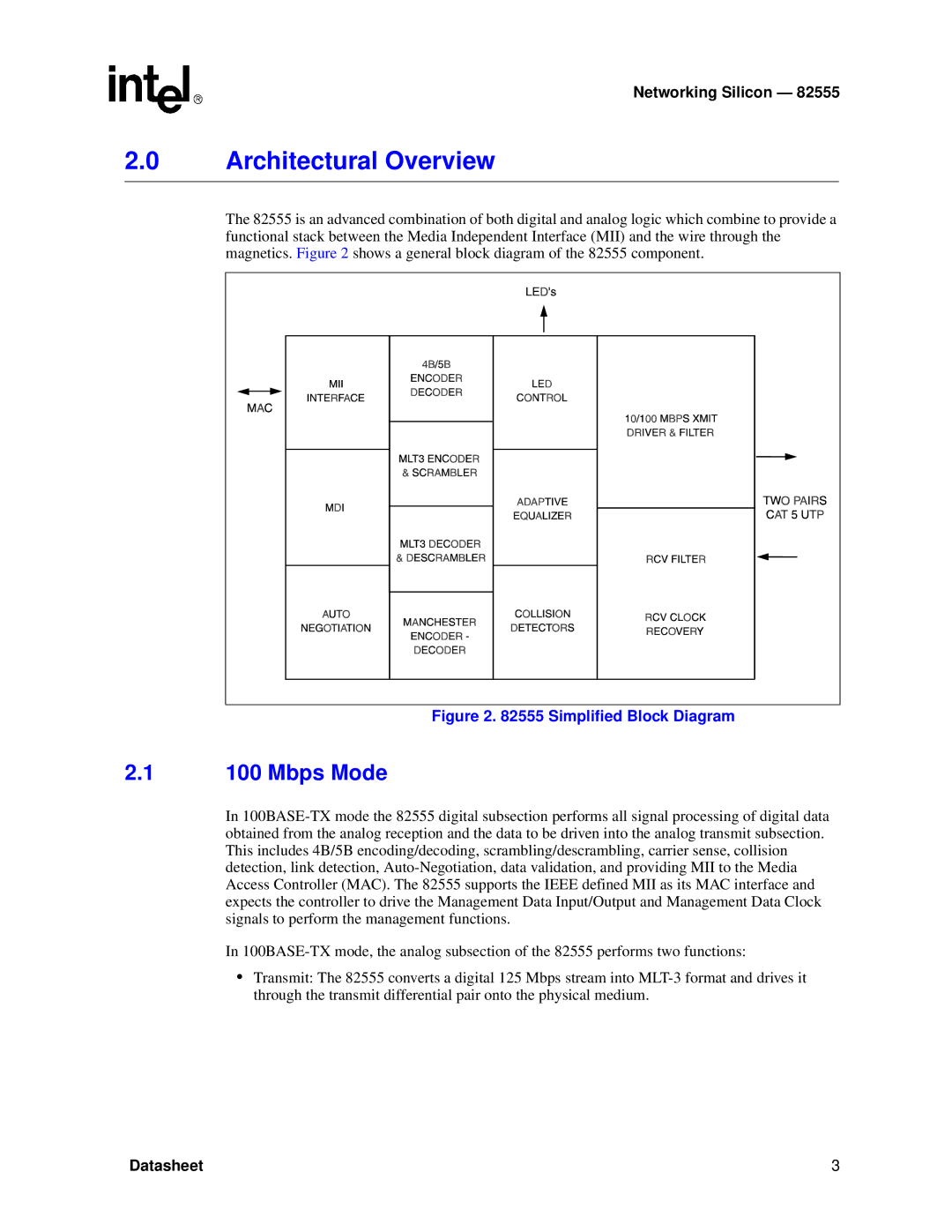

The 82555 is an advanced combination of both digital and analog logic which combine to provide a functional stack between the Media Independent Interface (MII) and the wire through the magnetics. Figure 2 shows a general block diagram of the 82555 component.

Figure 2. 82555 Simplified Block Diagram

2.1100 Mbps Mode

In 100BASE-TX mode the 82555 digital subsection performs all signal processing of digital data obtained from the analog reception and the data to be driven into the analog transmit subsection. This includes 4B/5B encoding/decoding, scrambling/descrambling, carrier sense, collision detection, link detection, Auto-Negotiation, data validation, and providing MII to the Media Access Controller (MAC). The 82555 supports the IEEE defined MII as its MAC interface and expects the controller to drive the Management Data Input/Output and Management Data Clock signals to perform the management functions.

In 100BASE-TX mode, the analog subsection of the 82555 performs two functions:

•Transmit: The 82555 converts a digital 125 Mbps stream into MLT-3 format and drives it through the transmit differential pair onto the physical medium.