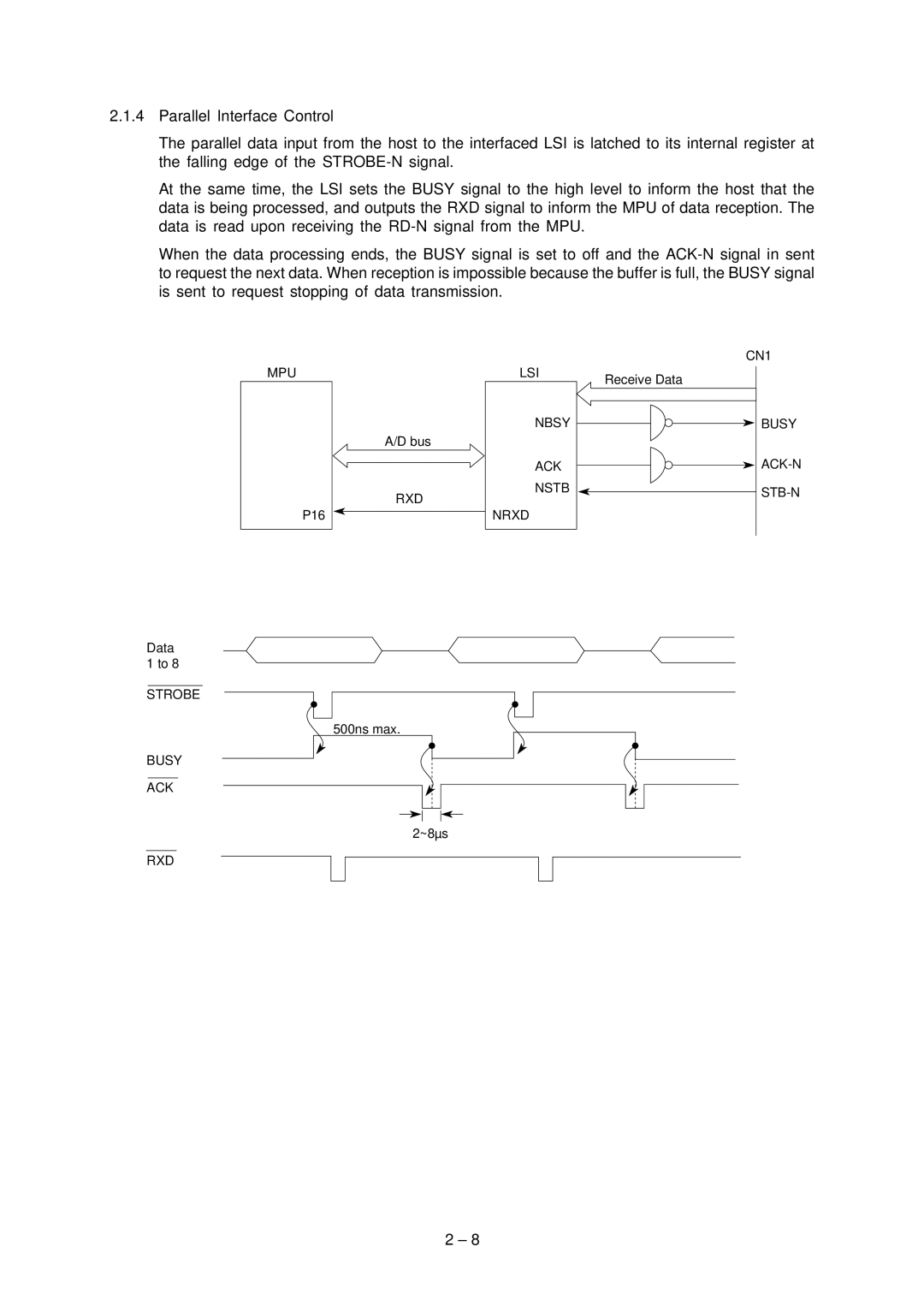

2.1.4Parallel Interface Control

The parallel data input from the host to the interfaced LSI is latched to its internal register at the falling edge of the

At the same time, the LSI sets the BUSY signal to the high level to inform the host that the data is being processed, and outputs the RXD signal to inform the MPU of data reception. The data is read upon receiving the

When the data processing ends, the BUSY signal is set to off and the

MPU

P16

LSI |

NBSY |

A/D bus |

ACK |

NSTB |

RXD |

NRXD |

CN1

Receive Data

BUSY

Data 1 to 8

STROBE

500ns max.

BUSY

ACK

2~8µs

RXD

2 – 8