7.6 BADR4

(Does not apply to

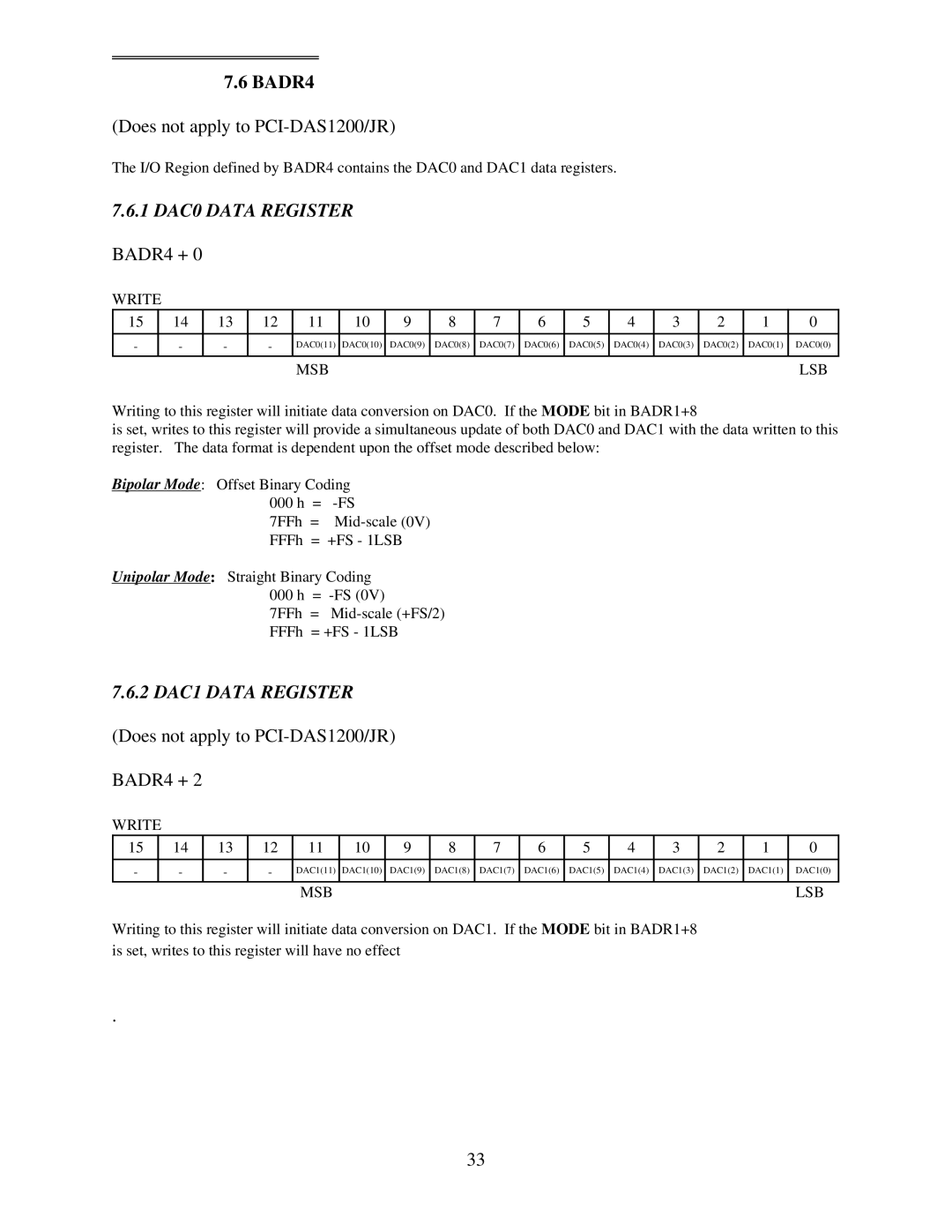

The I/O Region defined by BADR4 contains the DAC0 and DAC1 data registers.

7.6.1 DAC0 DATA REGISTER

BADR4 + 0

WRITE

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- | - | - | - | DAC0(11) | DAC0(10) | DAC0(9) | DAC0(8) | DAC0(7) | DAC0(6) | DAC0(5) | DAC0(4) | DAC0(3) | DAC0(2) | DAC0(1) | DAC0(0) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MSB |

|

|

|

|

|

|

|

|

|

| LSB |

Writing to this register will initiate data conversion on DAC0. If the MODE bit in BADR1+8

is set, writes to this register will provide a simultaneous update of both DAC0 and DAC1 with the data written to this register. The data format is dependent upon the offset mode described below:

Bipolar Mode: Offset Binary Coding

000 h =

7FFh =

FFFh = +FS - 1LSB

Unipolar Mode: Straight Binary Coding

000 h =

7FFh =

FFFh = +FS - 1LSB

7.6.2 DAC1 DATA REGISTER

(Does not apply to PCI-DAS1200/JR)

BADR4 + 2

WRITE

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

- | - | - | - | DAC1(11) | DAC1(10) | DAC1(9) | DAC1(8) | DAC1(7) | DAC1(6) | DAC1(5) | DAC1(4) | DAC1(3) | DAC1(2) | DAC1(1) | DAC1(0) |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| MSB |

|

|

|

|

|

|

|

|

|

| LSB |

Writing to this register will initiate data conversion on DAC1. If the MODE bit in BADR1+8 is set, writes to this register will have no effect

.

33