7.3.4 CALIBRATION REGISTER

As mentioned before, direct register level programming should be attempted only by extremely experienced register level programmers. This is true for

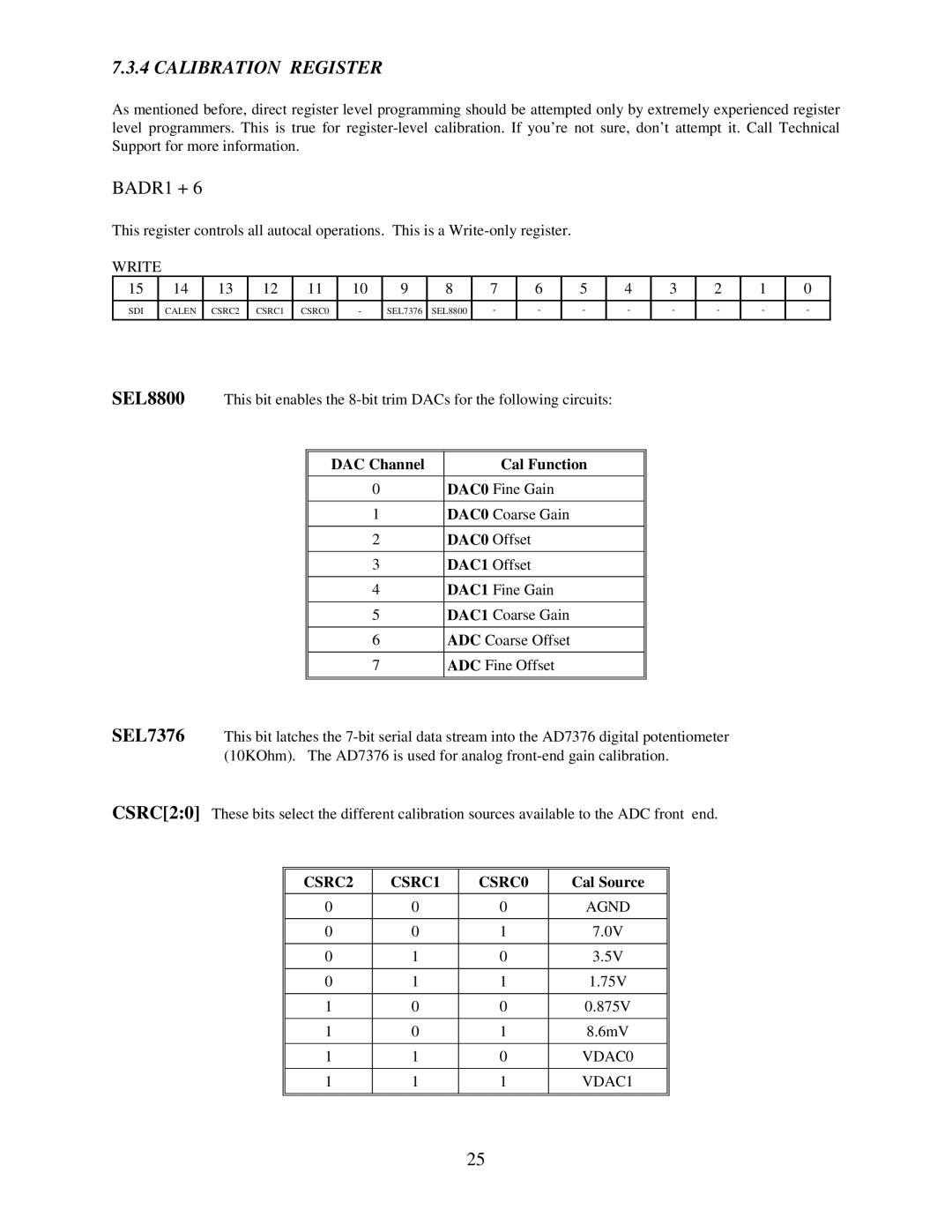

BADR1 + 6

This register controls all autocal operations. This is a

WRITE

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SDI | CALEN | CSRC2 | CSRC1 | CSRC0 | - | SEL7376 | SEL8800 | - | - | - | - | - | - | - | - |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

SEL8800 This bit enables the

DAC Channel | Cal Function |

|

|

0 | DAC0 Fine Gain |

|

|

1 | DAC0 Coarse Gain |

|

|

2 | DAC0 Offset |

|

|

3 | DAC1 Offset |

|

|

4 | DAC1 Fine Gain |

|

|

5 | DAC1 Coarse Gain |

|

|

6 | ADC Coarse Offset |

|

|

7 | ADC Fine Offset |

|

|

|

|

SEL7376 This bit latches the

CSRC[2:0] These bits select the different calibration sources available to the ADC front end.

CSRC2 | CSRC1 | CSRC0 | Cal Source |

|

|

|

|

0 | 0 | 0 | AGND |

|

|

|

|

0 | 0 | 1 | 7.0V |

|

|

|

|

0 | 1 | 0 | 3.5V |

|

|

|

|

0 | 1 | 1 | 1.75V |

|

|

|

|

1 | 0 | 0 | 0.875V |

|

|

|

|

1 | 0 | 1 | 8.6mV |

|

|

|

|

1 | 1 | 0 | VDAC0 |

|

|

|

|

1 | 1 | 1 | VDAC1 |

|

|

|

|

|

|

|

|

25