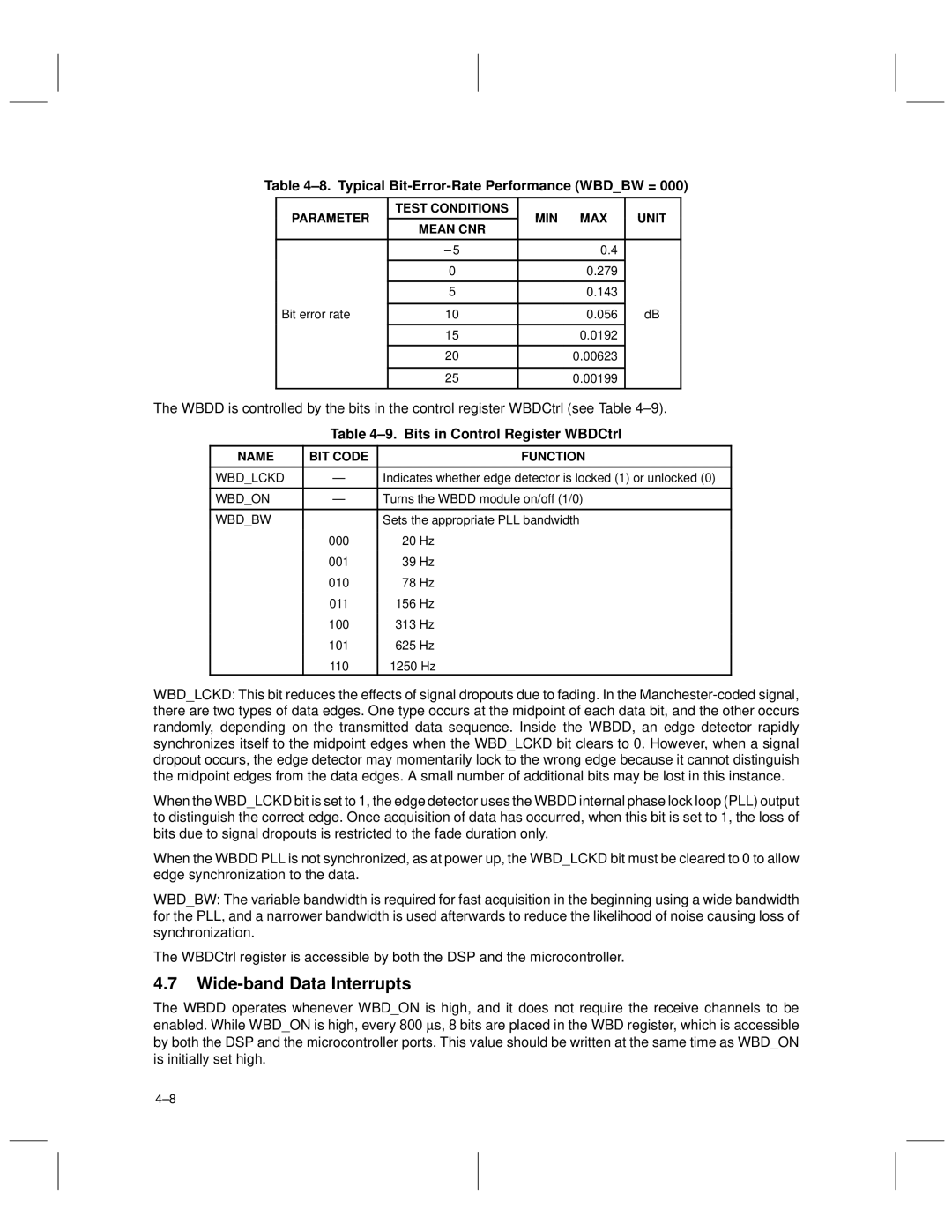

Table 4±8. Typical Bit-Error-Rate Performance (WBD_BW = 000)

PARAMETER | TEST CONDITIONS | MIN MAX | UNIT | |

| ||||

MEAN CNR | ||||

|

|

| ||

|

|

|

| |

| ± 5 | 0.4 |

| |

|

|

|

| |

| 0 | 0.279 |

| |

|

|

|

| |

| 5 | 0.143 |

| |

Bit error rate |

|

| dB | |

10 | 0.056 | |||

|

|

|

| |

| 15 | 0.0192 |

| |

|

|

|

| |

| 20 | 0.00623 |

| |

|

|

|

| |

| 25 | 0.00199 |

| |

|

|

|

|

The WBDD is controlled by the bits in the control register WBDCtrl (see Table 4±9).

Table 4±9. Bits in Control Register WBDCtrl

NAME | BIT CODE | FUNCTION |

|

|

|

WBD_LCKD | Ð | Indicates whether edge detector is locked (1) or unlocked (0) |

|

|

|

WBD_ON | Ð | Turns the WBDD module on/off (1/0) |

|

|

|

WBD_BW |

| Sets the appropriate PLL bandwidth |

| 000 | 20 Hz |

| 001 | 39 Hz |

| 010 | 78 Hz |

| 011 | 156 Hz |

| 100 | 313 Hz |

| 101 | 625 Hz |

| 110 | 1250 Hz |

WBD_LCKD: This bit reduces the effects of signal dropouts due to fading. In the

When the WBD_LCKD bit is set to 1, the edge detector uses the WBDD internal phase lock loop (PLL) output to distinguish the correct edge. Once acquisition of data has occurred, when this bit is set to 1, the loss of bits due to signal dropouts is restricted to the fade duration only.

When the WBDD PLL is not synchronized, as at power up, the WBD_LCKD bit must be cleared to 0 to allow edge synchronization to the data.

WBD_BW: The variable bandwidth is required for fast acquisition in the beginning using a wide bandwidth for the PLL, and a narrower bandwidth is used afterwards to reduce the likelihood of noise causing loss of synchronization.

The WBDCtrl register is accessible by both the DSP and the microcontroller.

4.7Wide-band Data Interrupts

The WBDD operates whenever WBD_ON is high, and it does not require the receive channels to be enabled. While WBD_ON is high, every 800 μs, 8 bits are placed in the WBD register, which is accessible by both the DSP and the microcontroller ports. This value should be written at the same time as WBD_ON is initially set high.

4±8