4.9Auxiliary DACs, LCD Contrast Converter

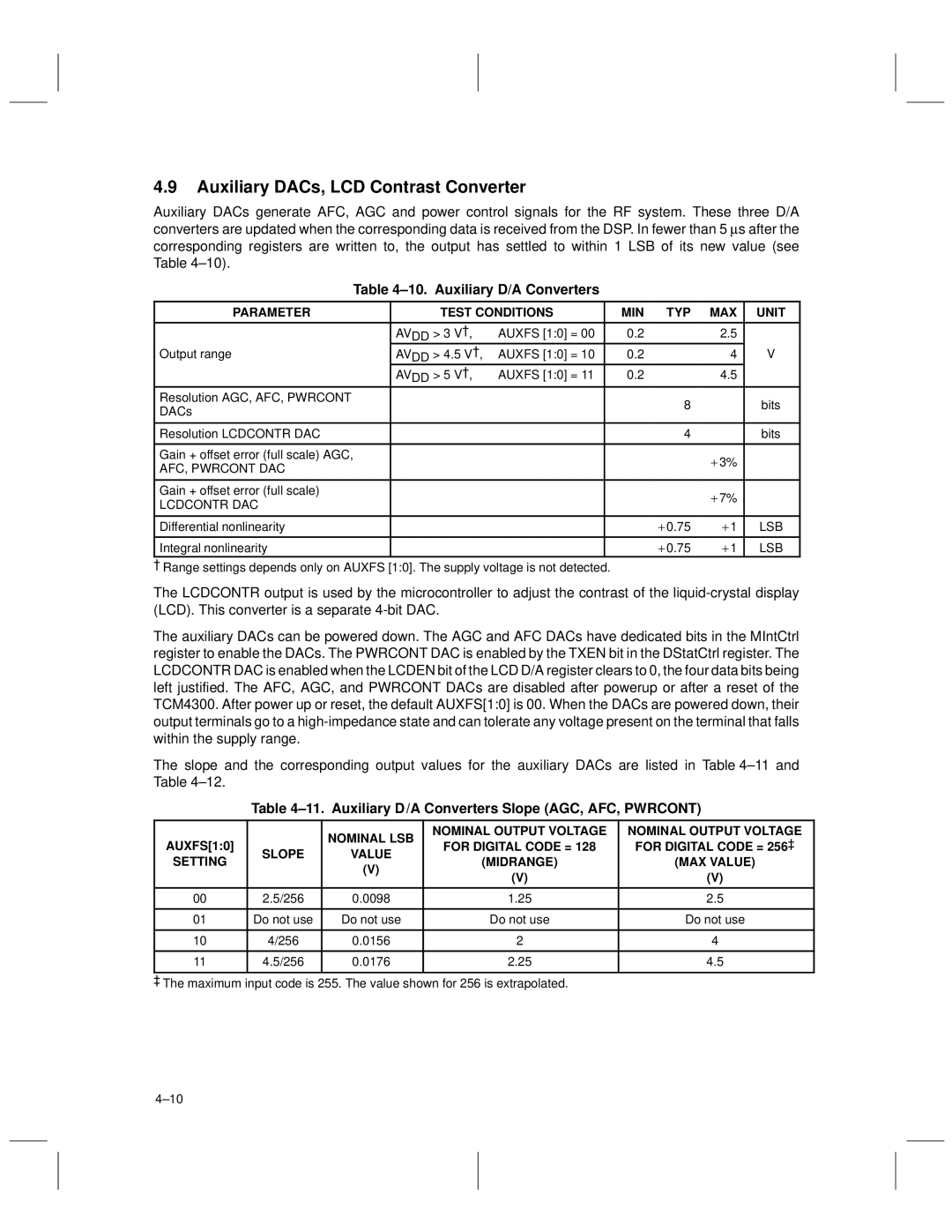

Auxiliary DACs generate AFC, AGC and power control signals for the RF system. These three D/A converters are updated when the corresponding data is received from the DSP. In fewer than 5 μs after the corresponding registers are written to, the output has settled to within 1 LSB of its new value (see Table 4±10).

Table 4±10. Auxiliary D/A Converters

PARAMETER | TEST CONDITIONS | MIN TYP | MAX | UNIT | |

|

|

|

|

|

|

| AVDD > 3 V² , | AUXFS [1:0] = 00 | 0.2 | 2.5 |

|

Output range | AVDD > 4.5 V² , | AUXFS [1:0] = 10 | 0.2 | 4 | V |

| AVDD > 5 V² , | AUXFS [1:0] = 11 | 0.2 | 4.5 |

|

Resolution AGC, AFC, PWRCONT |

|

| 8 |

| bits |

DACs |

|

|

| ||

|

|

|

|

| |

|

|

|

|

|

|

Resolution LCDCONTR DAC |

|

| 4 |

| bits |

|

|

|

|

|

|

Gain + offset error (full scale) AGC, |

|

|

| ± 3% |

|

AFC, PWRCONT DAC |

|

|

|

| |

|

|

|

|

| |

|

|

|

|

|

|

Gain + offset error (full scale) |

|

|

| ± 7% |

|

LCDCONTR DAC |

|

|

|

| |

|

|

|

|

| |

|

|

|

|

|

|

Differential nonlinearity |

|

| ± 0.75 | ± 1 | LSB |

|

|

|

|

|

|

Integral nonlinearity |

|

| ± 0.75 | ± 1 | LSB |

² Range settings depends only on AUXFS [1:0]. The supply voltage is not detected.

The LCDCONTR output is used by the microcontroller to adjust the contrast of the

The auxiliary DACs can be powered down. The AGC and AFC DACs have dedicated bits in the MIntCtrl register to enable the DACs. The PWRCONT DAC is enabled by the TXEN bit in the DStatCtrl register. The LCDCONTR DAC is enabled when the LCDEN bit of the LCD D/A register clears to 0, the four data bits being left justified. The AFC, AGC, and PWRCONT DACs are disabled after powerup or after a reset of the TCM4300. After power up or reset, the default AUXFS[1:0] is 00. When the DACs are powered down, their output terminals go to a

The slope and the corresponding output values for the auxiliary DACs are listed in Table 4±11 and Table 4±12.

Table 4±11. Auxiliary D /A Converters Slope (AGC, AFC, PWRCONT)

|

| NOMINAL LSB | NOMINAL OUTPUT VOLTAGE | NOMINAL OUTPUT VOLTAGE | |

AUXFS[1:0] |

| FOR DIGITAL CODE = 128 | FOR DIGITAL CODE = 256³ | ||

SLOPE | VALUE | ||||

SETTING | (MIDRANGE) | (MAX VALUE) | |||

| (V) | ||||

|

| (V) | (V) | ||

|

|

| |||

|

|

|

|

| |

00 | 2.5/256 | 0.0098 | 1.25 | 2.5 | |

|

|

|

|

| |

01 | Do not use | Do not use | Do not use | Do not use | |

|

|

|

|

| |

10 | 4/256 | 0.0156 | 2 | 4 | |

|

|

|

|

| |

11 | 4.5/256 | 0.0176 | 2.25 | 4.5 | |

|

|

|

|

|

³ The maximum input code is 255. The value shown for 256 is extrapolated.

4±10