Data Manual

SLWS010F

TCM4300 Data Manual

Important Notice

Contents

Mechanical Data ±1

List of Illustrations

List of Tables

Features

Introduction

TCM4300 Functional Block Diagram

Pin Assignments

PZ Package TOP View

VSS

Fmrxen

Terminal Functions

Terminal Description Name

Dsprw

Dspstrbl

Dvdd

Dvss

Mcds

MTS1

Mclkin

Mcrw

Scen

Sint

Synclk

Syndta

Power Rating Above TA = 25C

Dissipation Rating Table

Package

Derating Factor

Reference Characteristics

Power Consumption

Recommended Operating Conditions

Terminal Impedance

RXIP, RXIN, RXQP, and Rxqn Inputs Avdd = 3 V, 4.5 V, 5

Function MIN TYP² MAX Unit

Parameter Test Conditions MIN TYP MAX Unit

Auxiliary D/A Converters

Transmit I and Q Channel Outputs

Parameter MIN TYP MAX Unit

RSSI/Battery A/D Converter

Auxiliary D/A Converters Slope AGC, AFC, Pwrcont

Auxiliary D/A Converters Slope Lcdcontr

Nominal LSB Nominal Output Voltage

Transmit TX Channel Frequency Response Digital Mode

Transmit TX Channel Frequency Response Analog Mode

Page

Mclkout

Mclkout Timing Requirements see ±1 and Note

VOH VOL

Parameter Alternate MIN MAX Unit

Mcds

Mcrw

MCA4±MCA0 MCD7±MCD0 Mccsh Mccsl

Parameter Alternate MIN MAX Unit Symbol

MCA4±MCA0

MCA4±MCA0 MCD7±MCD0

Twdho

Motorola 16-Bit Read Cycle, MTS 10 =

MCA0±MCA4 MCD0±MCD7 Mccsh Mccsl

MCA0±MCA4

Mcrw MCA0±MCA4

MCD0±MCD7 Mccsh Mccsl

10% ThR / W ThWA

Dspcsl

Dspstrbl

Dsprw

Dspa Dspd

±11. TCM4300 to DSP Interface Write Cycle

±12

±1. TCM4300 Receive Channel Control Signals

Control Signal Analog Mode Digital Mode

Mode Fmvox Iqrxen Fmrxen

Data Transfer

±2. RXIP, RXIN, RXQP, and Rxqn Inputs Avdd = 3 V, 4.5 V, 5

Transmit Section

Modulation error percentage +100 s %

±5. Transmit TX I and Q Channel Outputs

±6. Transmit TX Channel Frequency Response Digital Mode

Transmit Burst Operation Digital Mode

±7. Transmit TX Channel Frequency Response Analog Mode

±1. Power Ramp-Up/Ramp-Down TIming Diagram

Transmit I And Q Output Level

Wide-Band Data Demodulator

±8. Typical Bit-Error-Rate Performance Wbdbw =

Wide-band Data Interrupts

±9. Bits in Control Register WBDCtrl

Parameter Test Conditions MIN MAX Unit Mean CNR

Wide-band Data Demodulator General Information

WBD

±10. Auxiliary D/A Converters

Auxiliary DACs, LCD Contrast Converter

±11. Auxiliary D /A Converters Slope AGC, AFC, Pwrcont

RSSI, Battery Monitor

±13. RSSI/Battery A/D Converter

Timing And Clock Generation

±12. Auxiliary D /A Converters Slope Lcdcontr

Clock Generation

Speech-Codec Clock Generation

Microcontroller Clock

Sample Interrupt Sint

Phase-Adjustment Strategy

Mclkin

RCO

Mclken

Frequency Synthesizer Interface

Clkpol Numclks Lowval

Highval

MSB/LSB First

Syndta

±14. Synthesizer Control Fields

Name Description

Power Control Port

15. External Power Control Signals

Name Suggested External Application Reset

Synclk Syndta SYNLE1 SYNLE0 Synrdy

Iqrxen Txen Mode

WBD Wbdon

OUT1

Fmrxen Scen

Microcontroller-DSP Communications

Dint

Fifo a Fifo B

Cint DSP

Microcontroller Register Map

±16. Microcontroller Register Map

±17. Microcontroller Register Definitions

Wide-Band Data/Control Register

Addr Name Category

Microcontroller Status and Control Registers

BIT Name Function Reset Value

±18. WBDCtrl Register

LCD Contrast

±19. MStatCtrl Register Bits

LDC D/A

Lcden

±20. DSP Register Map

DSP Register Map

±21. DSP Register Definitions

Wide-Band Data Registers

Base Station Offset Register

Dspcsl TCM4300 Dsprw Dspstrbl Sint Cint Bdint

DSP Strb INT

DSP Status and Control Registers

±22. DStatCtrl Register Bits

Reset

Power-On Reset

Internal Reset State

±23. Power-On Reset Register Initialization

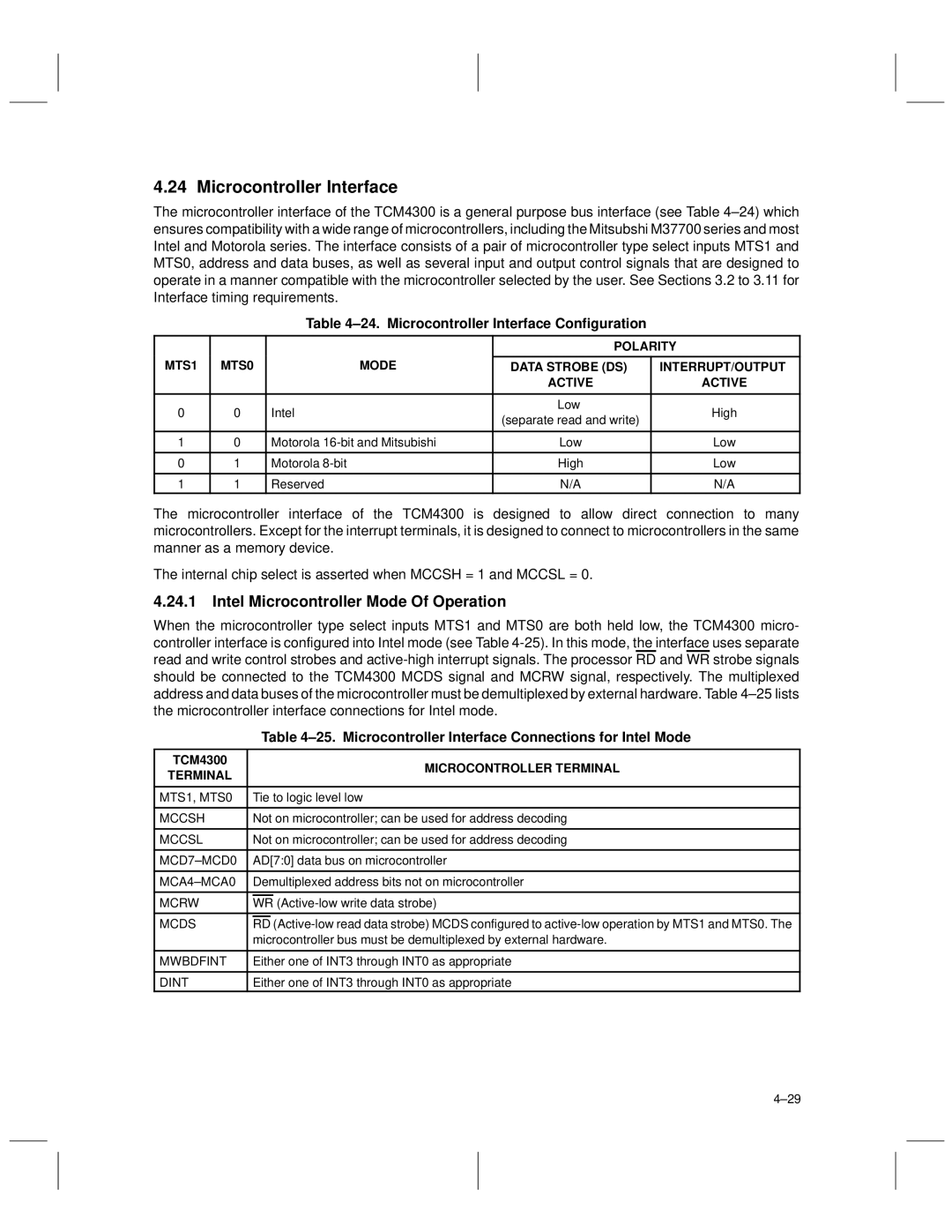

Intel Microcontroller Mode Of Operation

±24. Microcontroller Interface Configuration

±25. Microcontroller Interface Connections for Intel Mode

Microcontroller Interface

Mitsubishi Microcontroller Mode of Operation

Motorola Microcontroller Mode of Operation

Mcrw Mcds

IRQ NMI Dint

CS3

±32

Mechanical Data

PZ S-PQFP-G100

Important Notice