www.ti.com | Ethernet Media Access Controller (EMAC) Registers |

5.21Receive Multicast/Broadcast/Promiscuous Channel Enable Register

(RXMBPENABLE)

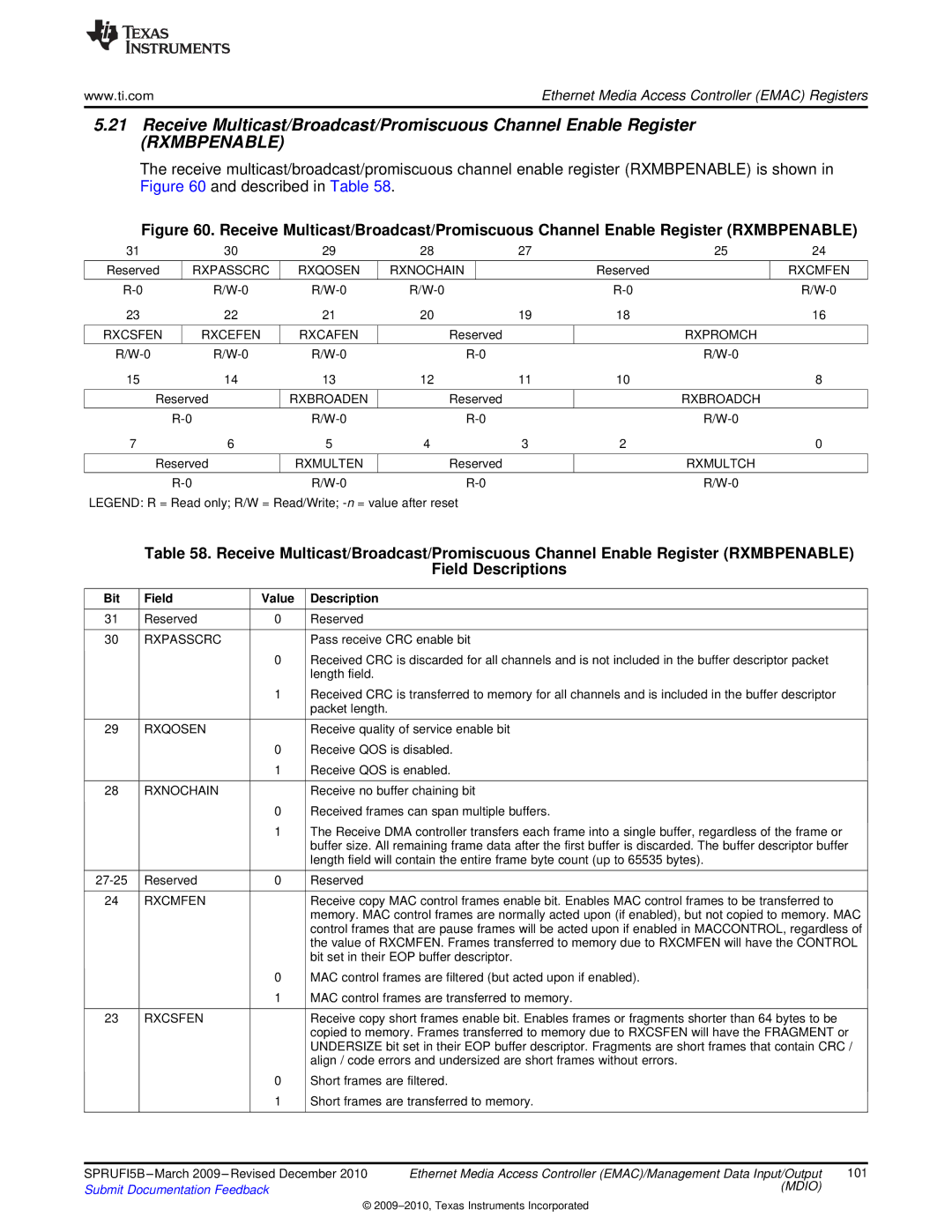

The receive multicast/broadcast/promiscuous channel enable register (RXMBPENABLE) is shown in Figure 60 and described in Table 58.

Figure 60. Receive Multicast/Broadcast/Promiscuous Channel Enable Register (RXMBPENABLE)

31 | 30 | 29 | 28 |

| 27 |

| 25 | 24 | |

Reserved |

| RXPASSCRC | RXQOSEN | RXNOCHAIN |

|

| Reserved |

| RXCMFEN |

|

|

| |||||||

23 | 22 | 21 | 20 |

| 19 | 18 |

| 16 | |

|

|

|

|

|

|

|

|

|

|

RXCSFEN |

| RXCEFEN | RXCAFEN | Reserved |

|

| RXPROMCH |

| |

|

|

|

| ||||||

15 | 14 | 13 | 12 |

| 11 | 10 |

| 8 | |

|

|

|

|

|

|

|

|

| |

Reserved | RXBROADEN | Reserved |

|

| RXBROADCH |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

7 | 6 | 5 | 4 |

| 3 | 2 |

| 0 | |

|

|

|

|

|

|

|

|

| |

Reserved | RXMULTEN | Reserved |

|

| RXMULTCH |

| |||

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||||

LEGEND: R = Read only; R/W = Read/Write;

Table 58. Receive Multicast/Broadcast/Promiscuous Channel Enable Register (RXMBPENABLE)

Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

31 | Reserved | 0 | Reserved |

|

|

|

|

30 | RXPASSCRC |

| Pass receive CRC enable bit |

|

| 0 | Received CRC is discarded for all channels and is not included in the buffer descriptor packet |

|

|

| length field. |

|

| 1 | Received CRC is transferred to memory for all channels and is included in the buffer descriptor |

|

|

| packet length. |

|

|

|

|

29 | RXQOSEN |

| Receive quality of service enable bit |

|

| 0 | Receive QOS is disabled. |

|

| 1 | Receive QOS is enabled. |

|

|

|

|

28 | RXNOCHAIN |

| Receive no buffer chaining bit |

|

| 0 | Received frames can span multiple buffers. |

|

| 1 | The Receive DMA controller transfers each frame into a single buffer, regardless of the frame or |

|

|

| buffer size. All remaining frame data after the first buffer is discarded. The buffer descriptor buffer |

|

|

| length field will contain the entire frame byte count (up to 65535 bytes). |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

24 | RXCMFEN |

| Receive copy MAC control frames enable bit. Enables MAC control frames to be transferred to |

|

|

| memory. MAC control frames are normally acted upon (if enabled), but not copied to memory. MAC |

|

|

| control frames that are pause frames will be acted upon if enabled in MACCONTROL, regardless of |

|

|

| the value of RXCMFEN. Frames transferred to memory due to RXCMFEN will have the CONTROL |

|

|

| bit set in their EOP buffer descriptor. |

|

| 0 | MAC control frames are filtered (but acted upon if enabled). |

|

| 1 | MAC control frames are transferred to memory. |

|

|

|

|

23 | RXCSFEN |

| Receive copy short frames enable bit. Enables frames or fragments shorter than 64 bytes to be |

|

|

| copied to memory. Frames transferred to memory due to RXCSFEN will have the FRAGMENT or |

|

|

| UNDERSIZE bit set in their EOP buffer descriptor. Fragments are short frames that contain CRC / |

|

|

| align / code errors and undersized are short frames without errors. |

|

| 0 | Short frames are filtered. |

|

| 1 | Short frames are transferred to memory. |

|

|

|

|

SPRUFI5B

Submit Documentation Feedback | (MDIO) |

|

©