www.ti.com | EMAC Control Module Registers |

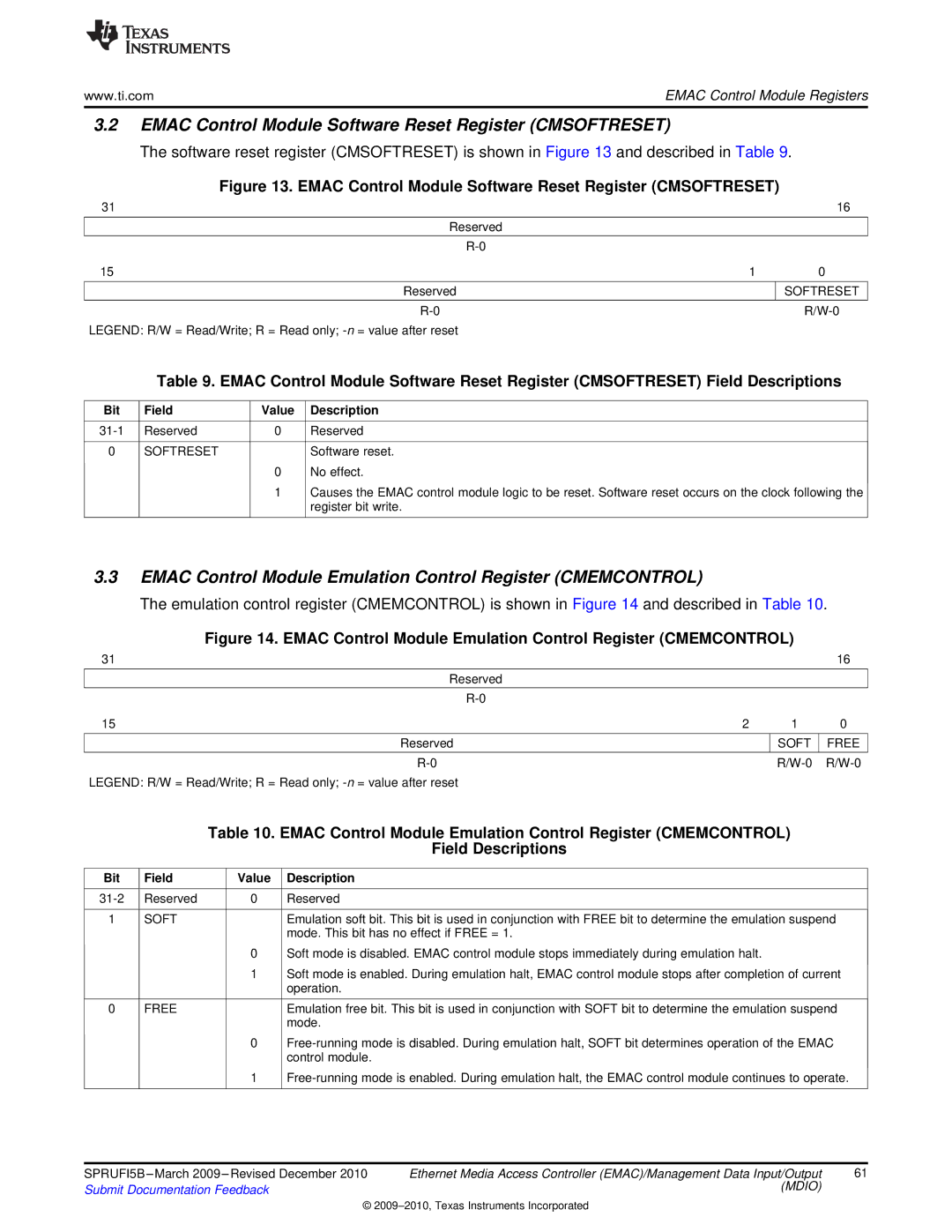

3.2EMAC Control Module Software Reset Register (CMSOFTRESET)

The software reset register (CMSOFTRESET) is shown in Figure 13 and described in Table 9.

Figure 13. EMAC Control Module Software Reset Register (CMSOFTRESET)

31 |

| 16 |

Reserved |

|

|

|

|

|

|

| |

15 | 1 | 0 |

|

|

|

Reserved |

| SOFTRESET |

|

|

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 9. EMAC Control Module Software Reset Register (CMSOFTRESET) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

0 | SOFTRESET |

| Software reset. |

|

| 0 | No effect. |

|

| 1 | Causes the EMAC control module logic to be reset. Software reset occurs on the clock following the |

|

|

| register bit write. |

|

|

|

|

3.3EMAC Control Module Emulation Control Register (CMEMCONTROL)

The emulation control register (CMEMCONTROL) is shown in Figure 14 and described in Table 10.

Figure 14. EMAC Control Module Emulation Control Register (CMEMCONTROL)

31 |

|

| 16 |

Reserved |

|

|

|

|

|

| |

15 | 2 | 1 | 0 |

|

|

|

|

Reserved |

| SOFT | FREE |

|

|

|

|

|

LEGEND: R/W = Read/Write; R = Read only;

Table 10. EMAC Control Module Emulation Control Register (CMEMCONTROL)

Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

1 | SOFT |

| Emulation soft bit. This bit is used in conjunction with FREE bit to determine the emulation suspend |

|

|

| mode. This bit has no effect if FREE = 1. |

|

| 0 | Soft mode is disabled. EMAC control module stops immediately during emulation halt. |

|

| 1 | Soft mode is enabled. During emulation halt, EMAC control module stops after completion of current |

|

|

| operation. |

|

|

|

|

0 | FREE |

| Emulation free bit. This bit is used in conjunction with SOFT bit to determine the emulation suspend |

|

|

| mode. |

|

| 0 | |

|

|

| control module. |

|

| 1 | |

|

|

|

|

SPRUFI5B

Submit Documentation Feedback | (MDIO) |

|

©