EMAC Control Module Registers | www.ti.com |

3.4EMAC Control Module Interrupt Control Register (CMINTCTRL)

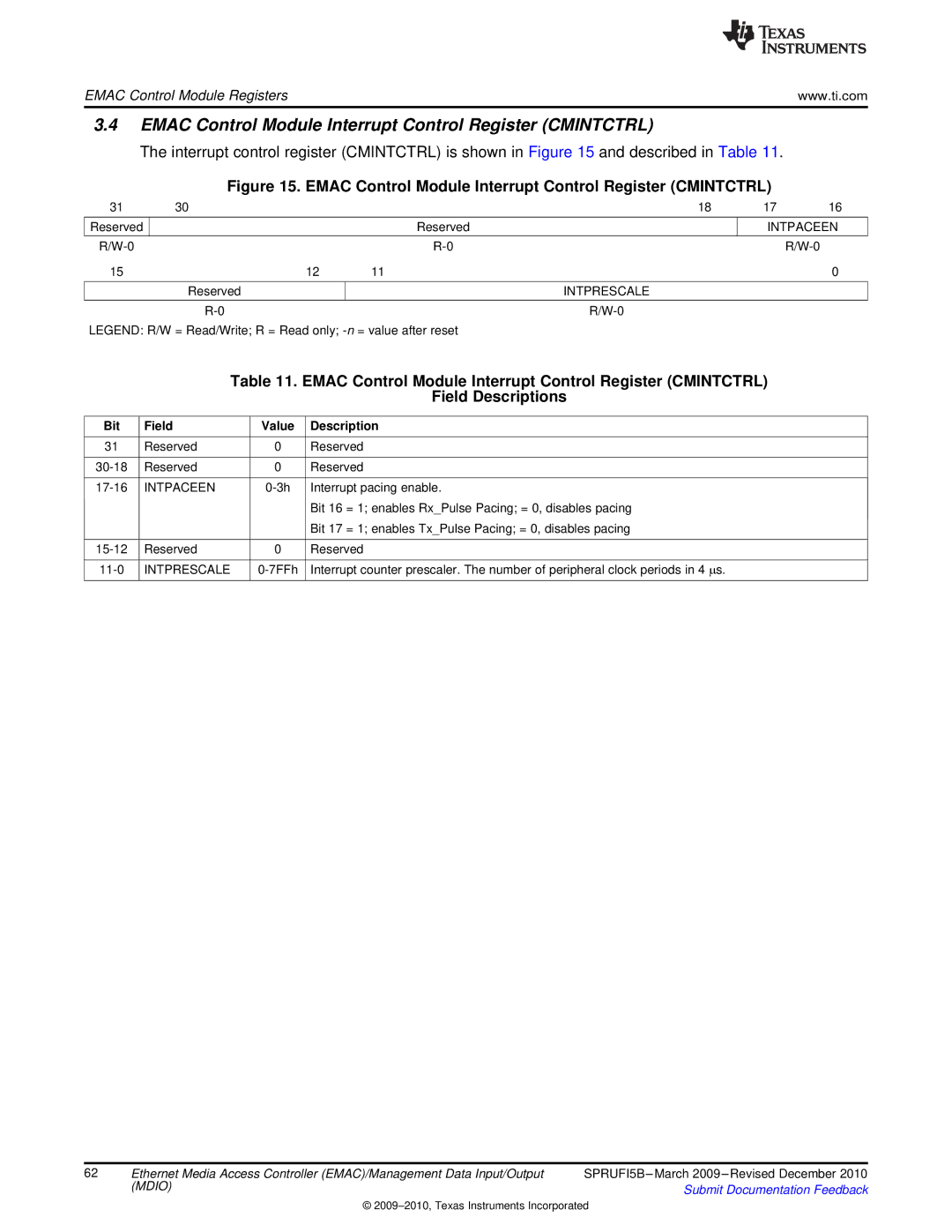

The interrupt control register (CMINTCTRL) is shown in Figure 15 and described in Table 11.

Figure 15. EMAC Control Module Interrupt Control Register (CMINTCTRL)

31 | 30 |

| 18 | 17 | 16 |

Reserved |

| Reserved |

| INTPACEEN | |

|

|

|

|

|

|

|

|

| |||

15 | 12 | 11 |

|

| 0 |

|

|

|

|

|

|

| Reserved |

| INTPRESCALE |

|

|

|

|

|

|

|

|

|

|

|

| ||

LEGEND: R/W = Read/Write; R = Read only; |

|

|

| ||

|

| Table 11. EMAC Control Module Interrupt Control Register (CMINTCTRL) | ||

|

|

|

| Field Descriptions |

|

|

|

|

|

Bit | Field |

| Value | Description |

|

|

|

|

|

31 | Reserved |

| 0 | Reserved |

|

|

|

|

|

Reserved |

| 0 | Reserved | |

|

|

|

|

|

INTPACEEN |

| Interrupt pacing enable. | ||

|

|

|

| Bit 16 = 1; enables Rx_Pulse Pacing; = 0, disables pacing |

|

|

|

| Bit 17 = 1; enables Tx_Pulse Pacing; = 0, disables pacing |

|

|

|

|

|

Reserved |

| 0 | Reserved | |

|

|

|

|

|

INTPRESCALE |

| Interrupt counter prescaler. The number of peripheral clock periods in 4 μs. | ||

|

|

|

|

|

62 Ethernet Media Access Controller (EMAC)/Management Data Input/Output SPRUFI5B

(MDIO) | Submit Documentation Feedback |

|

©