MDIO Registers | www.ti.com |

4.6MDIO Link Status Change Interrupt (Masked) Register (LINKINTMASKED)

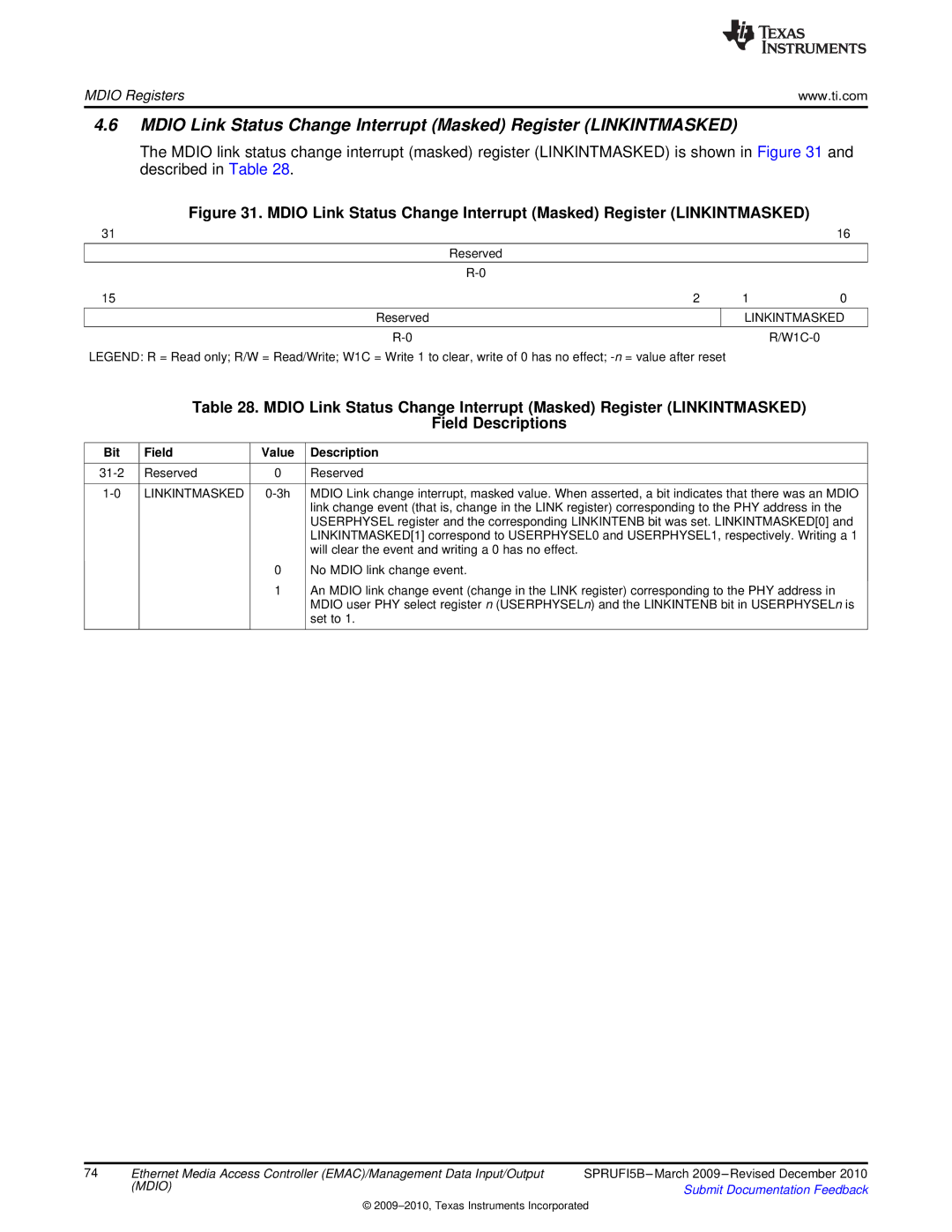

The MDIO link status change interrupt (masked) register (LINKINTMASKED) is shown in Figure 31 and described in Table 28.

Figure 31. MDIO Link Status Change Interrupt (Masked) Register (LINKINTMASKED)

31 |

|

| 16 |

| Reserved |

|

|

|

|

|

|

|

|

| |

15 | 2 | 1 | 0 |

|

|

| |

Reserved |

| LINKINTMASKED | |

|

|

|

|

|

| ||

LEGEND: R = Read only; R/W = Read/Write; W1C = Write 1 to clear, write of 0 has no effect;

Table 28. MDIO Link Status Change Interrupt (Masked) Register (LINKINTMASKED)

Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

| Reserved | 0 | Reserved |

|

|

|

|

LINKINTMASKED | MDIO Link change interrupt, masked value. When asserted, a bit indicates that there was an MDIO | ||

|

|

| link change event (that is, change in the LINK register) corresponding to the PHY address in the |

|

|

| USERPHYSEL register and the corresponding LINKINTENB bit was set. LINKINTMASKED[0] and |

|

|

| LINKINTMASKED[1] correspond to USERPHYSEL0 and USERPHYSEL1, respectively. Writing a 1 |

|

|

| will clear the event and writing a 0 has no effect. |

|

| 0 | No MDIO link change event. |

|

| 1 | An MDIO link change event (change in the LINK register) corresponding to the PHY address in |

|

|

| MDIO user PHY select register n (USERPHYSELn) and the LINKINTENB bit in USERPHYSELn is |

|

|

| set to 1. |

|

|

|

|

74 Ethernet Media Access Controller (EMAC)/Management Data Input/Output SPRUFI5B

(MDIO) | Submit Documentation Feedback |

|

©