www.ti.com | Architecture |

2.18 Power Management

Each of the three main components of the EMAC peripheral can independently be placed in

The power conservation modes available for each of the three components of the EMAC/MDIO peripheral are:

•Idle/Disabled state. This mode stops the clocks going to the peripheral, and prevents all the register accesses. After reenabling the peripheral from this idle state, all the registers values prior to setting into the disabled state are restored, and data transmission can proceed. No reinitialization is required.

•Synchronized reset. This state is similar to the

For more information on the use of the processor Power and Sleep Controller (PSC), see the TMS320DM365 Digital Media

2.19 Emulation Considerations

NOTE: For correct operation, the EMAC and EMAC control module must both be suspended. Thus, the EMCONTROL and CMEMCONTROL registers must be configured alike.

EMAC emulation control is implemented for compatibility with other peripherals. The SOFT and FREE bits in the emulation control register (EMCONTROL) allow EMAC operation to be suspended. Additionally, emulation control is also implemented in the EMAC control module with the EMAC control module emulation control register (CMEMCONTROL) to allow the EMAC control module activity to be suspended.

When the emulation suspend state is entered, the EMAC stops processing receive and transmit frames at the next frame boundary. Any frame currently in reception or transmission is completed normally without suspension. For transmission, any complete or partial frame in the transmit cell FIFO is transmitted. For receive, frames that are detected by the EMAC after the suspend state is entered are ignored. No statistics are kept for ignored frames.

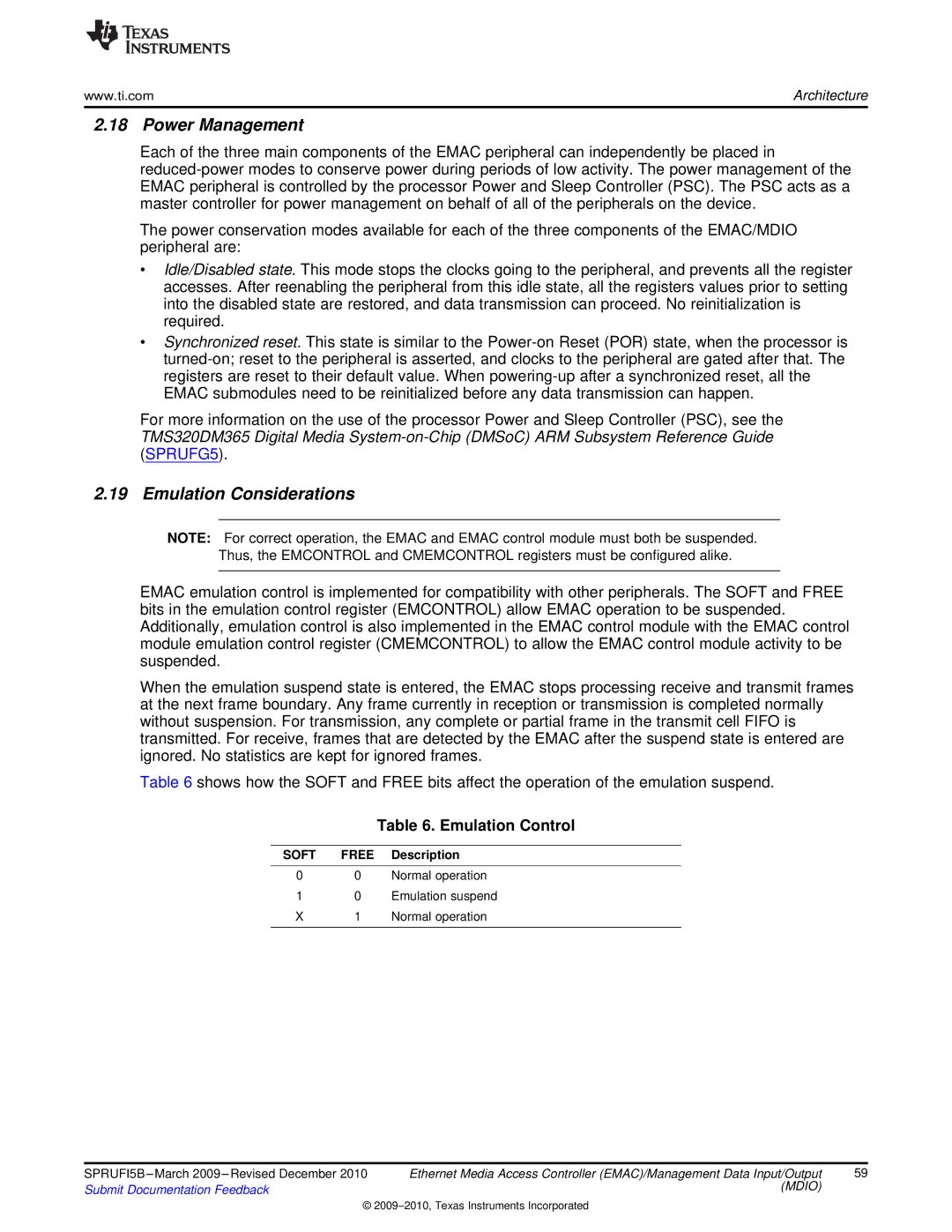

Table 6 shows how the SOFT and FREE bits affect the operation of the emulation suspend.

Table 6. Emulation Control

SOFT FREE Description

00 Normal operation

10 Emulation suspend

X | 1 | Normal operation |

SPRUFI5B

Submit Documentation Feedback | (MDIO) |

|

©