Ethernet Media Access Controller (EMAC) Registers | www.ti.com |

5.41 Receive Pause Timer Register (RXPAUSE)

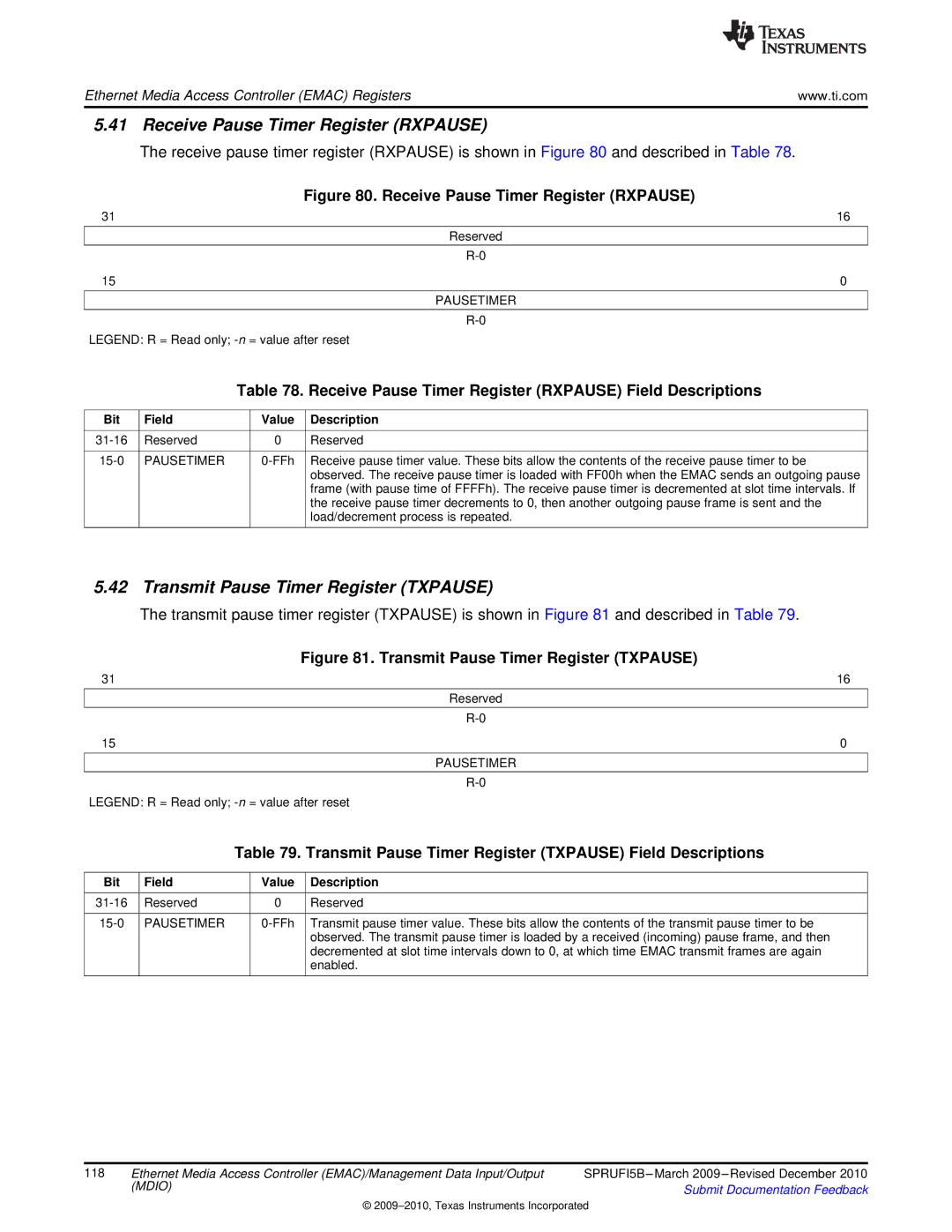

The receive pause timer register (RXPAUSE) is shown in Figure 80 and described in Table 78.

| Figure 80. Receive Pause Timer Register (RXPAUSE) |

31 | 16 |

|

|

| Reserved |

|

|

| |

15 | 0 |

PAUSETIMER

LEGEND: R = Read only;

Table 78. Receive Pause Timer Register (RXPAUSE) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

PAUSETIMER | Receive pause timer value. These bits allow the contents of the receive pause timer to be | ||

|

|

| observed. The receive pause timer is loaded with FF00h when the EMAC sends an outgoing pause |

|

|

| frame (with pause time of FFFFh). The receive pause timer is decremented at slot time intervals. If |

|

|

| the receive pause timer decrements to 0, then another outgoing pause frame is sent and the |

|

|

| load/decrement process is repeated. |

|

|

|

|

5.42 Transmit Pause Timer Register (TXPAUSE)

The transmit pause timer register (TXPAUSE) is shown in Figure 81 and described in Table 79.

| Figure 81. Transmit Pause Timer Register (TXPAUSE) |

31 | 16 |

|

|

| Reserved |

| |

15 | 0 |

PAUSETIMER

LEGEND: R = Read only;

Table 79. Transmit Pause Timer Register (TXPAUSE) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

Reserved | 0 | Reserved | |

|

|

|

|

PAUSETIMER | Transmit pause timer value. These bits allow the contents of the transmit pause timer to be | ||

|

|

| observed. The transmit pause timer is loaded by a received (incoming) pause frame, and then |

|

|

| decremented at slot time intervals down to 0, at which time EMAC transmit frames are again |

|

|

| enabled. |

|

|

|

|

118 Ethernet Media Access Controller (EMAC)/Management Data Input/Output SPRUFI5B

(MDIO) | Submit Documentation Feedback |

|

©