www.ti.com | Architecture |

2.5.6.6ECC Generation

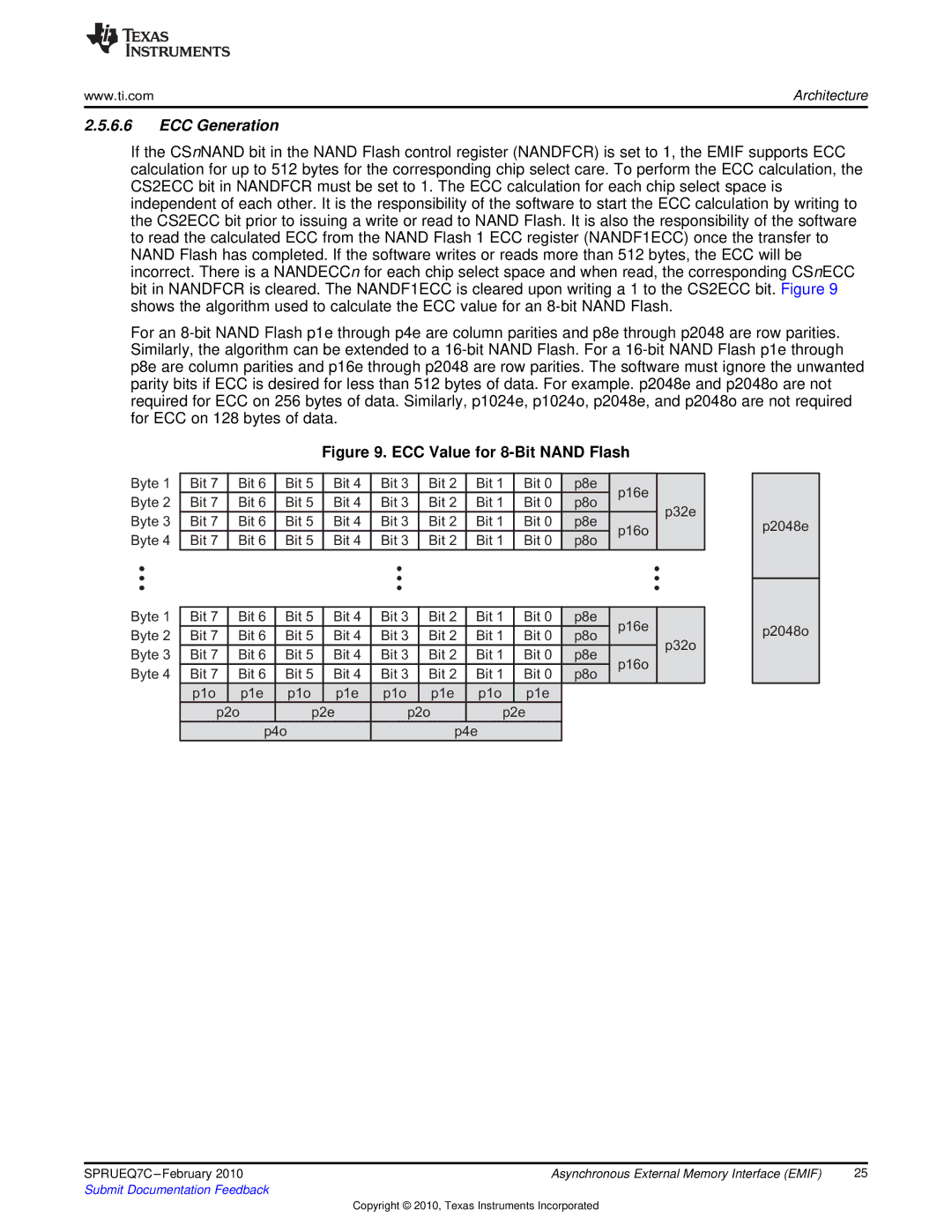

If the CSnNAND bit in the NAND Flash control register (NANDFCR) is set to 1, the EMIF supports ECC calculation for up to 512 bytes for the corresponding chip select care. To perform the ECC calculation, the CS2ECC bit in NANDFCR must be set to 1. The ECC calculation for each chip select space is independent of each other. It is the responsibility of the software to start the ECC calculation by writing to the CS2ECC bit prior to issuing a write or read to NAND Flash. It is also the responsibility of the software to read the calculated ECC from the NAND Flash 1 ECC register (NANDF1ECC) once the transfer to NAND Flash has completed. If the software writes or reads more than 512 bytes, the ECC will be incorrect. There is a NANDECCn for each chip select space and when read, the corresponding CSnECC bit in NANDFCR is cleared. The NANDF1ECC is cleared upon writing a 1 to the CS2ECC bit. Figure 9 shows the algorithm used to calculate the ECC value for an

For an

Figure 9. ECC Value for 8-Bit NAND Flash

Byte 1 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | p8e | p16e |

| |

Byte 2 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | p8o | p32e | ||

| ||||||||||||

Byte 3 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | p8e | p16o | ||

| ||||||||||||

Byte 4 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | p8o |

| ||

|

|

Byte 1 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | p8e |

Byte 2 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | p16e |

p8o | |||||||||

Byte 3 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | p32o |

p8e | |||||||||

Byte 4 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | p16o |

p8o | |||||||||

| p1o | p1e | p1o | p1e | p1o | p1e | p1o | p1e |

|

| p2o | p2e | p2o | p2e |

| ||||

|

| p4o |

|

| p4e |

|

| ||

p2048e |

p2048o |

SPRUEQ7C | Asynchronous External Memory Interface (EMIF) | 25 |

Submit Documentation Feedback |

|

|

Copyright © 2010, Texas Instruments Incorporated