www.ti.com | Registers |

4.4EMIF Interrupt Raw Register (EIRR)

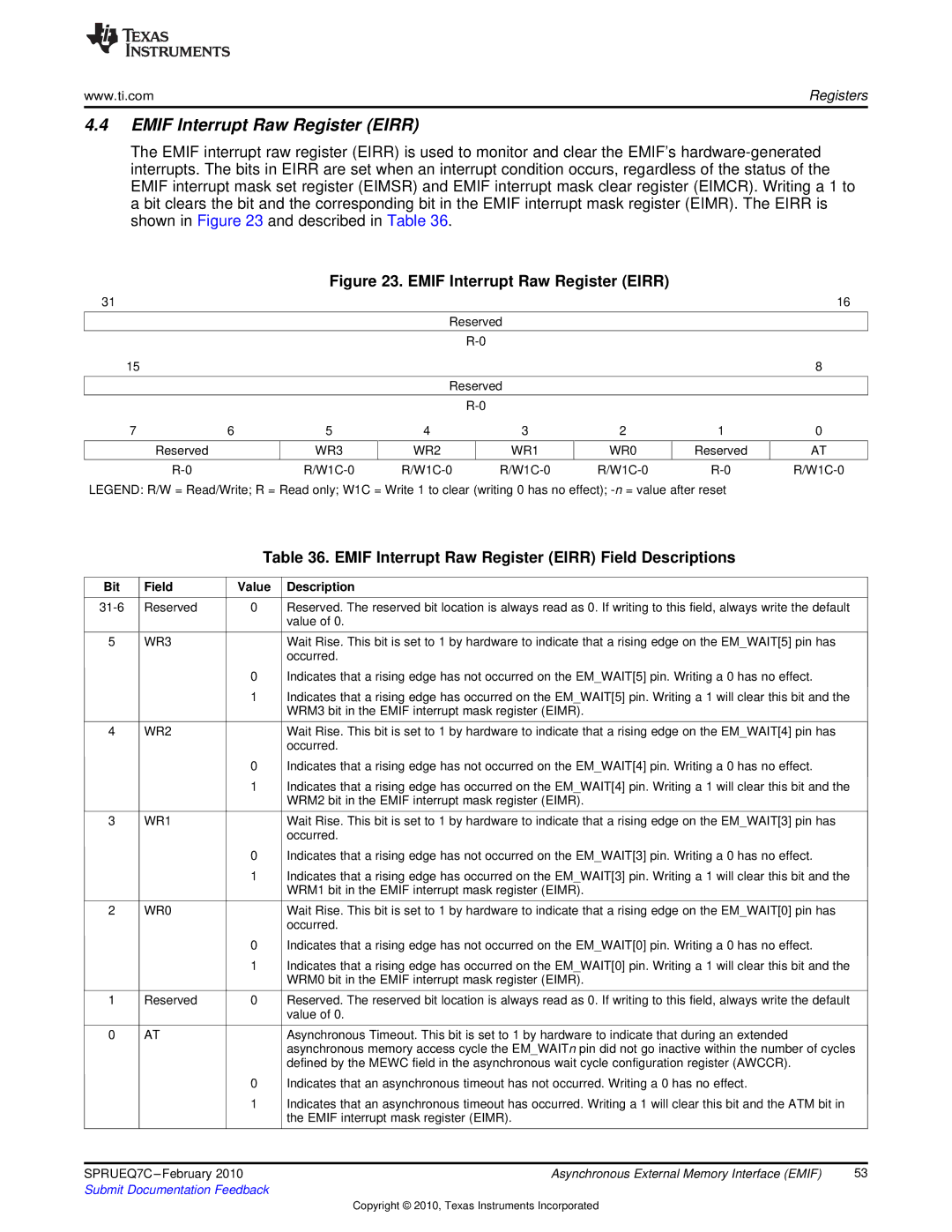

The EMIF interrupt raw register (EIRR) is used to monitor and clear the EMIF’s

|

| Figure 23. EMIF Interrupt Raw Register (EIRR) |

|

| ||||

31 |

|

|

|

|

|

|

| 16 |

|

|

|

|

|

|

| ||

|

|

| Reserved |

|

|

| ||

|

|

|

|

|

|

| ||

15 |

|

|

|

|

|

|

| 8 |

|

|

|

|

|

|

| ||

|

|

| Reserved |

|

|

| ||

|

|

|

|

|

|

| ||

7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

|

|

|

|

|

|

|

|

|

| Reserved | WR3 | WR2 |

| WR1 | WR0 | Reserved | AT |

|

|

|

|

|

|

|

|

|

|

| |||||||

LEGEND: R/W = Read/Write; R = Read only; W1C = Write 1 to clear (writing 0 has no effect);

Table 36. EMIF Interrupt Raw Register (EIRR) Field Descriptions

Bit | Field | Value | Description |

|

|

|

|

|

|

Reserved | 0 | Reserved. The reserved bit location is always read as 0. If writing to this field, always write the default |

| |

|

|

| value of 0. |

|

|

|

|

|

|

5 | WR3 |

| Wait Rise. This bit is set to 1 by hardware to indicate that a rising edge on the EM_WAIT[5] pin has |

|

|

|

| occurred. |

|

|

| 0 | Indicates that a rising edge has not occurred on the EM_WAIT[5] pin. Writing a 0 has no effect. |

|

|

| 1 | Indicates that a rising edge has occurred on the EM_WAIT[5] pin. Writing a 1 will clear this bit and the |

|

|

|

| WRM3 bit in the EMIF interrupt mask register (EIMR). |

|

|

|

|

|

|

4 | WR2 |

| Wait Rise. This bit is set to 1 by hardware to indicate that a rising edge on the EM_WAIT[4] pin has |

|

|

|

| occurred. |

|

|

| 0 | Indicates that a rising edge has not occurred on the EM_WAIT[4] pin. Writing a 0 has no effect. |

|

|

| 1 | Indicates that a rising edge has occurred on the EM_WAIT[4] pin. Writing a 1 will clear this bit and the |

|

|

|

| WRM2 bit in the EMIF interrupt mask register (EIMR). |

|

|

|

|

|

|

3 | WR1 |

| Wait Rise. This bit is set to 1 by hardware to indicate that a rising edge on the EM_WAIT[3] pin has |

|

|

|

| occurred. |

|

|

| 0 | Indicates that a rising edge has not occurred on the EM_WAIT[3] pin. Writing a 0 has no effect. |

|

|

| 1 | Indicates that a rising edge has occurred on the EM_WAIT[3] pin. Writing a 1 will clear this bit and the |

|

|

|

| WRM1 bit in the EMIF interrupt mask register (EIMR). |

|

|

|

|

|

|

2 | WR0 |

| Wait Rise. This bit is set to 1 by hardware to indicate that a rising edge on the EM_WAIT[0] pin has |

|

|

|

| occurred. |

|

|

| 0 | Indicates that a rising edge has not occurred on the EM_WAIT[0] pin. Writing a 0 has no effect. |

|

|

| 1 | Indicates that a rising edge has occurred on the EM_WAIT[0] pin. Writing a 1 will clear this bit and the |

|

|

|

| WRM0 bit in the EMIF interrupt mask register (EIMR). |

|

|

|

|

|

|

1 | Reserved | 0 | Reserved. The reserved bit location is always read as 0. If writing to this field, always write the default |

|

|

|

| value of 0. |

|

|

|

|

|

|

0 | AT |

| Asynchronous Timeout. This bit is set to 1 by hardware to indicate that during an extended |

|

|

|

| asynchronous memory access cycle the EM_WAITn pin did not go inactive within the number of cycles | |

|

|

| defined by the MEWC field in the asynchronous wait cycle configuration register (AWCCR). |

|

|

| 0 | Indicates that an asynchronous timeout has not occurred. Writing a 0 has no effect. |

|

|

| 1 | Indicates that an asynchronous timeout has occurred. Writing a 1 will clear this bit and the ATM bit in |

|

|

|

| the EMIF interrupt mask register (EIMR). |

|

|

|

|

|

|

|

|

|

|

|

SPRUEQ7C | Asynchronous External Memory Interface (EMIF) | 53 | ||

Submit Documentation Feedback |

|

| ||

Copyright © 2010, Texas Instruments Incorporated