Use Cases | www.ti.com |

3.2.2Meeting AC Timing Requirements for NAND Flash

When configuring the EMIF to interface to NAND Flash, you must consider the AC timing requirements of the NAND Flash as well as the AC timing requirements of the EMIF. These can be found in the data sheet for each respective device. The read and write asynchronous cycles are programmed separately in the asynchronous configuration register (ACFGn).

As described in Section 2.5.6, a NAND Flash access cycle is composed of a command, address, and data phases. The EMIF will not automatically generate these three phases to complete a NAND access with one transfer request. To complete a NAND access cycle, multiple single asynchronous access cycles must be completed by the EMIF. The command and address phases of a NAND Flash access cycle are asynchronous writes performed by the EMIF where as the data phase can be either an asynchronous write or a read depending on whether the NAND Flash is being programmed or read.

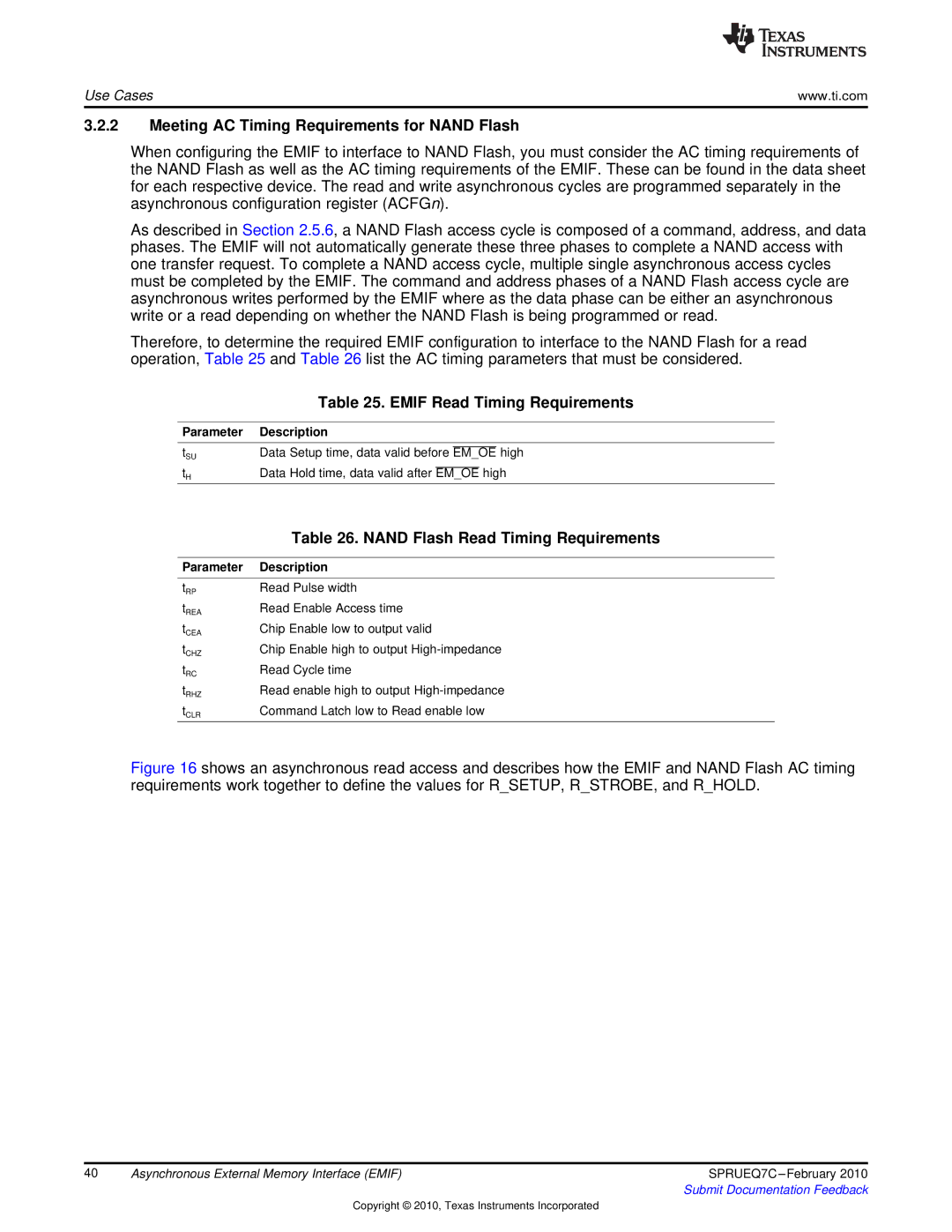

Therefore, to determine the required EMIF configuration to interface to the NAND Flash for a read operation, Table 25 and Table 26 list the AC timing parameters that must be considered.

| Table 25. EMIF Read Timing Requirements | ||||

|

| ||||

Parameter | Description | ||||

|

|

|

| ||

tSU | Data Setup time, data valid before |

|

| high | |

EM_OE | |||||

tH | Data Hold time, data valid after |

|

| high | |

EM_OE | |||||

| Table 26. NAND Flash Read Timing Requirements |

|

|

Parameter | Description |

|

|

tRP | Read Pulse width |

tREA | Read Enable Access time |

tCEA | Chip Enable low to output valid |

tCHZ | Chip Enable high to output |

tRC | Read Cycle time |

tRHZ | Read enable high to output |

tCLR | Command Latch low to Read enable low |

Figure 16 shows an asynchronous read access and describes how the EMIF and NAND Flash AC timing requirements work together to define the values for R_SETUP, R_STROBE, and R_HOLD.

40 | Asynchronous External Memory Interface (EMIF) | SPRUEQ7C |

|

| Submit Documentation Feedback |

Copyright © 2010, Texas Instruments Incorporated