Architecture | www.ti.com |

2.5.2Programmable Asynchronous Parameters

The EMIF allows a high degree of programmability for shaping asynchronous accesses. The programmable parameters are:

•Setup: The time between the beginning of a memory cycle (address valid) and the activation of the output enable or write enable strobe

•Strobe: The time between the activation and deactivation of output enable or write enable strobe.

•Hold: The time between the deactivation of output enable or write enable strobe and the end of the cycle, which may be indicated by an address change or the deactivation of the EM_CS signal.

Separate parameters are provided for read and write cycles. Each parameter is programmed in terms of EMIF clock cycles.

2.5.3Configuring the EMIF for Asynchronous Accesses

The operation of the EMIF'sasynchronous interface can be configured by programming the appropriate

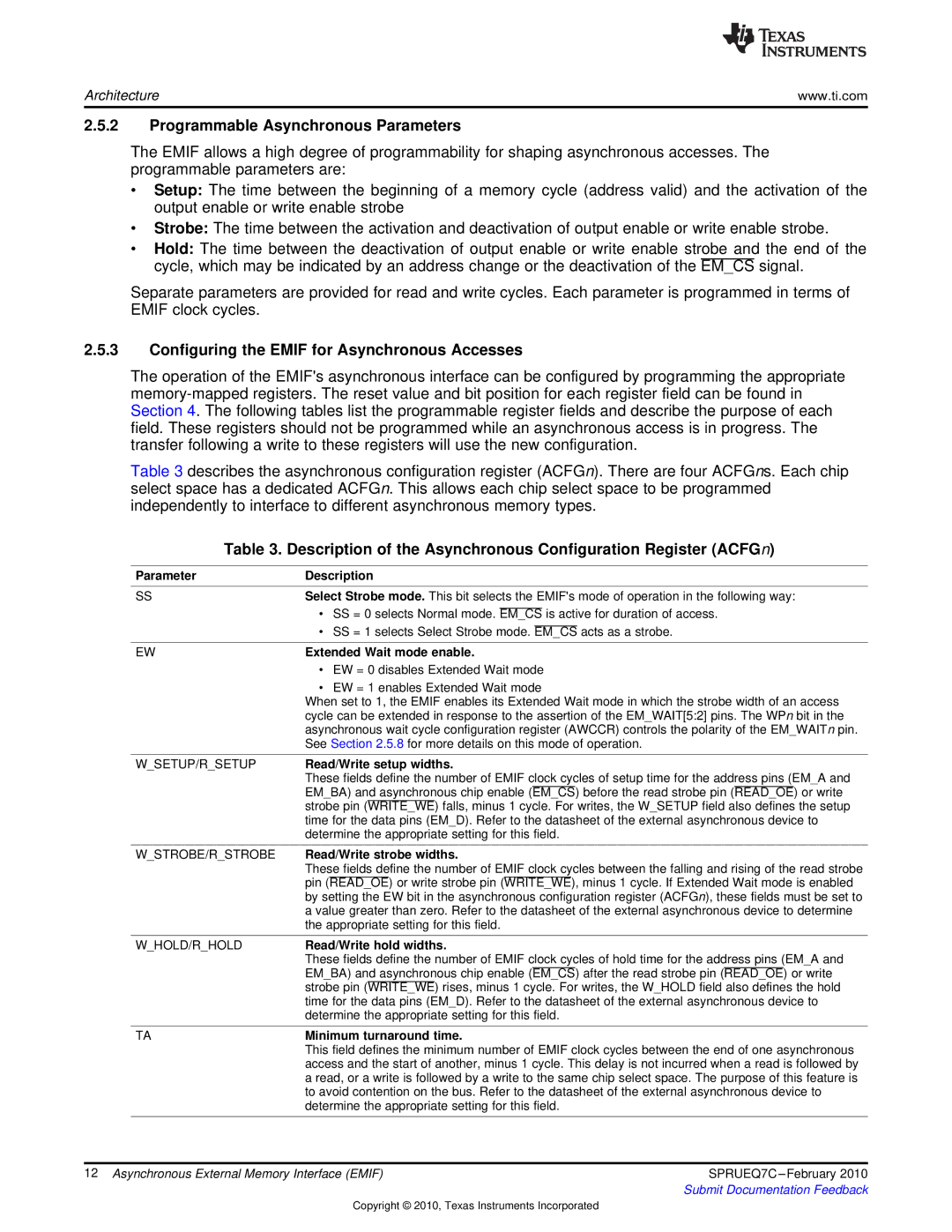

Table 3 describes the asynchronous configuration register (ACFGn). There are four ACFGns. Each chip select space has a dedicated ACFGn. This allows each chip select space to be programmed independently to interface to different asynchronous memory types.

| Table 3. Description of the Asynchronous Configuration Register (ACFGn) | ||||||||||||||||||

|

|

|

|

|

|

|

| ||||||||||||

| Parameter | Description |

|

|

|

|

| ||||||||||||

|

|

| |||||||||||||||||

| SS | Select Strobe mode. This bit selects the EMIF's mode of operation in the following way: | |||||||||||||||||

|

| • SS = 0 selects Normal mode. |

| is active for duration of access. | |||||||||||||||

|

| EM_CS | |||||||||||||||||

|

| • SS = 1 selects Select Strobe mode. |

|

| acts as a strobe. |

|

|

|

|

| |||||||||

|

| EM_CS |

|

|

|

|

| ||||||||||||

| EW | Extended Wait mode enable. |

|

|

|

|

| ||||||||||||

|

| • EW = 0 disables Extended Wait mode |

|

|

|

|

| ||||||||||||

|

| • EW = 1 enables Extended Wait mode |

|

|

|

|

| ||||||||||||

|

| When set to 1, the EMIF enables its Extended Wait mode in which the strobe width of an access | |||||||||||||||||

|

| cycle can be extended in response to the assertion of the EM_WAIT[5:2] pins. The WPn bit in the | |||||||||||||||||

|

| asynchronous wait cycle configuration register (AWCCR) controls the polarity of the EM_WAITn pin. | |||||||||||||||||

|

| See Section 2.5.8 for more details on this mode of operation. |

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

| W_SETUP/R_SETUP | Read/Write setup widths. |

|

|

|

|

| ||||||||||||

|

| These fields define the number of EMIF clock cycles of setup time for the address pins (EM_A and | |||||||||||||||||

|

| EM_BA) and asynchronous chip enable | (EM_CS) |

| before the read strobe pin | (READ_OE) | or write | ||||||||||||

|

| strobe pin | (WRITE_WE) | falls, minus 1 cycle. For writes, the W_SETUP field also defines the setup | |||||||||||||||

|

| time for the data pins (EM_D). Refer to the datasheet of the external asynchronous device to | |||||||||||||||||

|

| determine the appropriate setting for this field. |

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

| ||||||||

| W_STROBE/R_STROBE | Read/Write strobe widths. |

|

|

|

|

| ||||||||||||

|

| These fields define the number of EMIF clock cycles between the falling and rising of the read strobe | |||||||||||||||||

|

| pin |

| or write strobe pin |

|

|

|

|

|

|

| ||||||||

|

| (READ_OE) | (WRITE_WE), minus 1 cycle. If Extended Wait mode is enabled | ||||||||||||||||

|

| by setting the EW bit in the asynchronous configuration register (ACFGn), these fields must be set to | |||||||||||||||||

|

| a value greater than zero. Refer to the datasheet of the external asynchronous device to determine | |||||||||||||||||

|

| the appropriate setting for this field. |

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| ||||

| W_HOLD/R_HOLD | Read/Write hold widths. |

|

|

|

|

| ||||||||||||

|

| These fields define the number of EMIF clock cycles of hold time for the address pins (EM_A and | |||||||||||||||||

|

| EM_BA) and asynchronous chip enable | (EM_CS) |

| after the read strobe pin | (READ_OE) | or write | ||||||||||||

|

| strobe pin | (WRITE_WE) | rises, minus 1 cycle. For writes, the W_HOLD field also defines the hold | |||||||||||||||

|

| time for the data pins (EM_D). Refer to the datasheet of the external asynchronous device to | |||||||||||||||||

|

| determine the appropriate setting for this field. |

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| TA | Minimum turnaround time. |

|

|

|

|

| ||||||||||||

|

| This field defines the minimum number of EMIF clock cycles between the end of one asynchronous | |||||||||||||||||

|

| access and the start of another, minus 1 cycle. This delay is not incurred when a read is followed by | |||||||||||||||||

|

| a read, or a write is followed by a write to the same chip select space. The purpose of this feature is | |||||||||||||||||

|

| to avoid contention on the bus. Refer to the datasheet of the external asynchronous device to | |||||||||||||||||

|

| determine the appropriate setting for this field. |

|

|

|

|

| ||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

12 Asynchronous External Memory Interface (EMIF) | SPRUEQ7C | ||||||||||||||||||

|

|

|

|

|

|

|

|

|

|

|

|

|

|

| Submit Documentation Feedback | ||||

Copyright © 2010, Texas Instruments Incorporated