Architecture | www.ti.com |

2.5.4Read and Write Operations in Normal Mode

Normal mode is the asynchronous interface'sdefault mode of operation. The Normal mode is selected when the SS bit in the asynchronous configuration register (ACFGn) is cleared to 0. In this mode, the EM_CS signal operates as a chip enable signal, active throughout the duration of the memory access.

2.5.4.1Asynchronous Read Operations (Normal Mode)

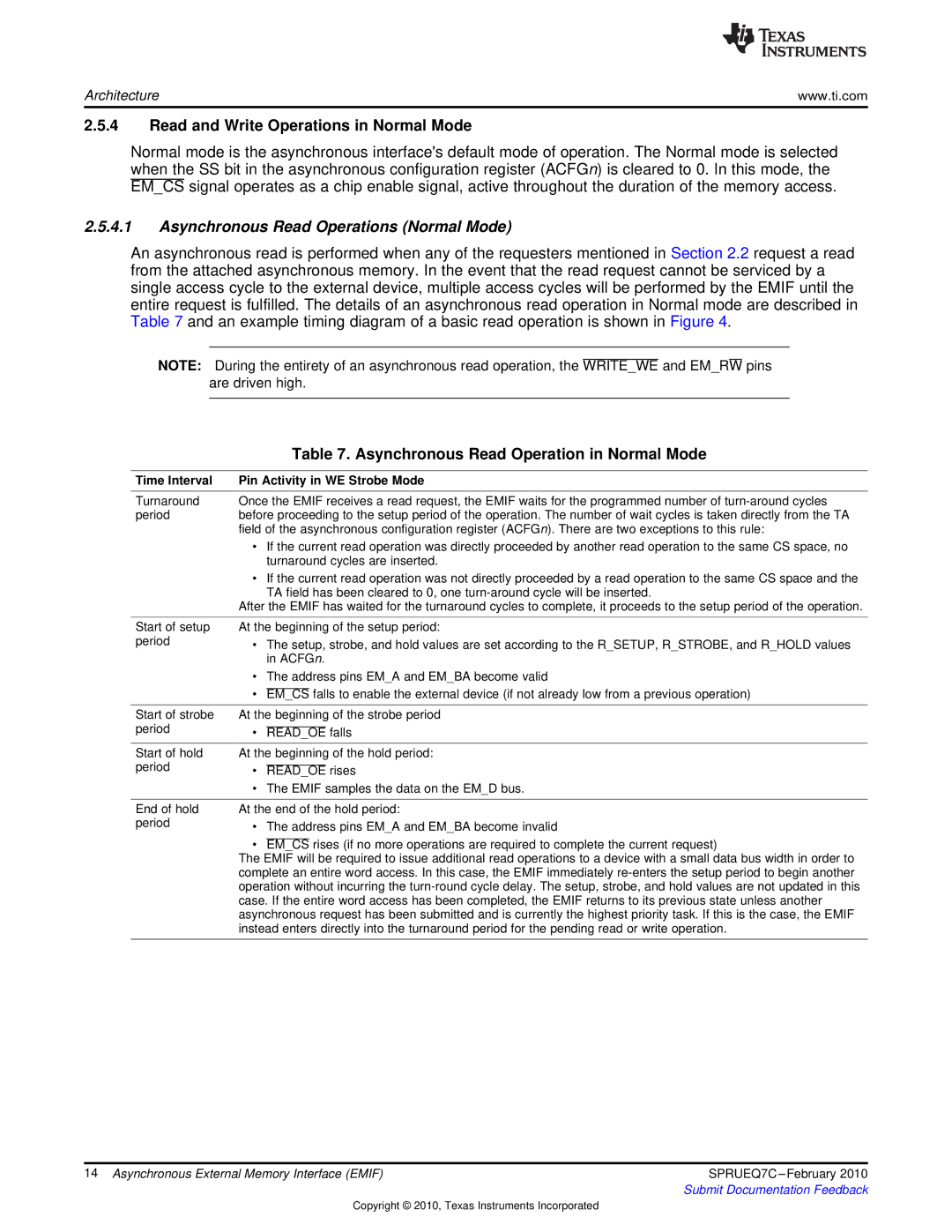

An asynchronous read is performed when any of the requesters mentioned in Section 2.2 request a read from the attached asynchronous memory. In the event that the read request cannot be serviced by a single access cycle to the external device, multiple access cycles will be performed by the EMIF until the entire request is fulfilled. The details of an asynchronous read operation in Normal mode are described in Table 7 and an example timing diagram of a basic read operation is shown in Figure 4.

NOTE: During the entirety of an asynchronous read operation, the WRITE_WE and EM_RW pins are driven high.

| Table 7. Asynchronous Read Operation in Normal Mode |

|

|

Time Interval | Pin Activity in WE Strobe Mode |

|

|

Turnaround | Once the EMIF receives a read request, the EMIF waits for the programmed number of |

period | before proceeding to the setup period of the operation. The number of wait cycles is taken directly from the TA |

| field of the asynchronous configuration register (ACFGn). There are two exceptions to this rule: |

•If the current read operation was directly proceeded by another read operation to the same CS space, no turnaround cycles are inserted.

•If the current read operation was not directly proceeded by a read operation to the same CS space and the TA field has been cleared to 0, one

After the EMIF has waited for the turnaround cycles to complete, it proceeds to the setup period of the operation.

Start of setup | At the beginning of the setup period: | ||||

period | • The setup, strobe, and hold values are set according to the R_SETUP, R_STROBE, and R_HOLD values | ||||

| |||||

|

| in ACFGn. | |||

| • The address pins EM_A and EM_BA become valid | ||||

| • |

| falls to enable the external device (if not already low from a previous operation) | ||

| EM_CS | ||||

Start of strobe | At the beginning of the strobe period | ||||

period |

|

|

|

| |

• READ_OE falls | |||||

| |||||

Start of hold | At the beginning of the hold period: | ||||

period |

|

|

|

| |

• READ_OE rises | |||||

| |||||

| • The EMIF samples the data on the EM_D bus. | ||||

|

|

| |||

End of hold | At the end of the hold period: | ||||

period | • The address pins EM_A and EM_BA become invalid | ||||

| |||||

| • |

| rises (if no more operations are required to complete the current request) | ||

| EM_CS | ||||

| The EMIF will be required to issue additional read operations to a device with a small data bus width in order to | ||||

| complete an entire word access. In this case, the EMIF immediately | ||||

| operation without incurring the | ||||

| case. If the entire word access has been completed, the EMIF returns to its previous state unless another | ||||

| asynchronous request has been submitted and is currently the highest priority task. If this is the case, the EMIF | ||||

| instead enters directly into the turnaround period for the pending read or write operation. | ||||

|

|

|

|

| |

14 Asynchronous External Memory Interface (EMIF) | SPRUEQ7C |

| Submit Documentation Feedback |

Copyright © 2010, Texas Instruments Incorporated