R

Chapter 5

Scratchpad RAM

The PicoBlaze™ microcontroller contains a

The scratchpad RAM is unaffected by a RESET Event.

Address Modes

The STORE and FETCH instructions support both direct and indirect addressing modes to access scratchpad RAM data.

Direct Addressing

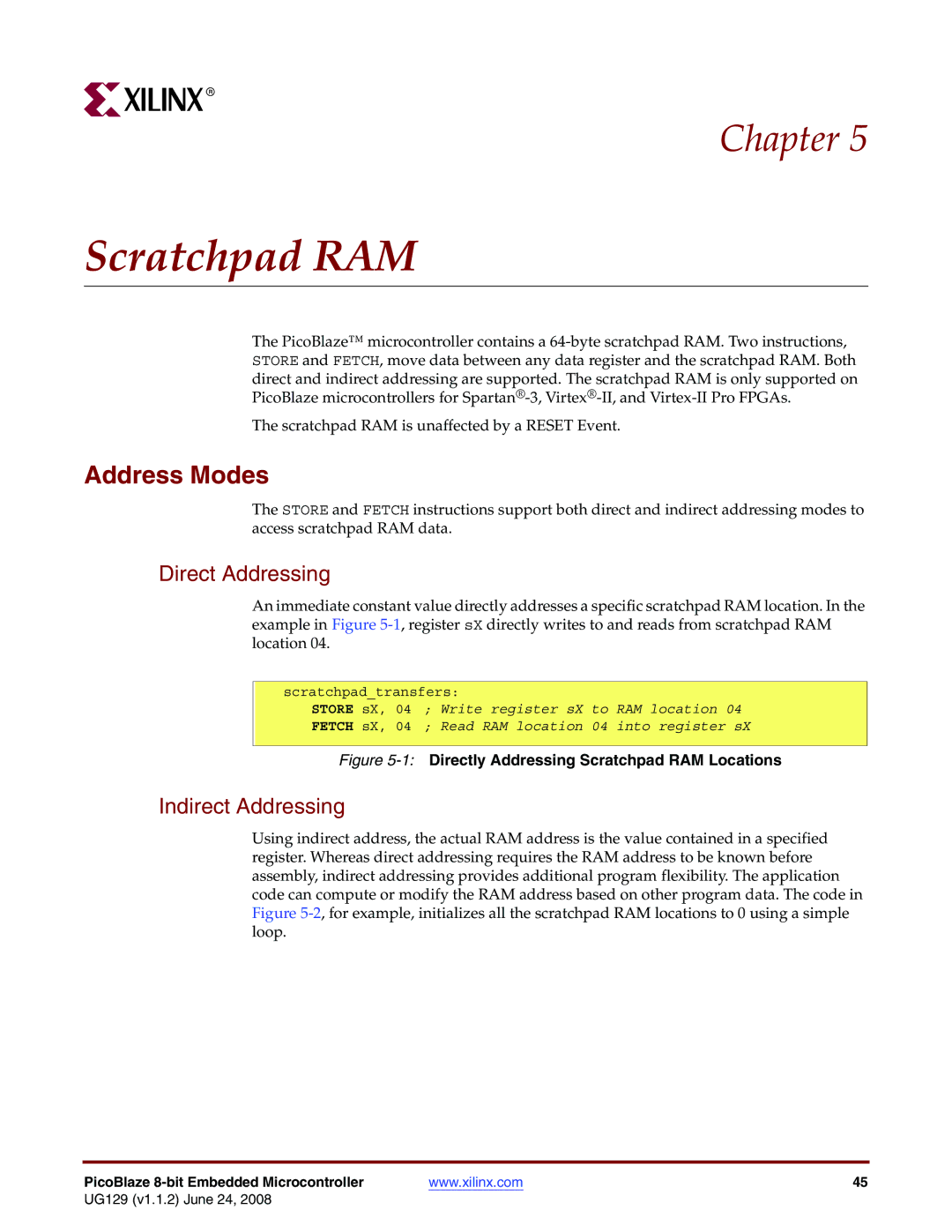

An immediate constant value directly addresses a specific scratchpad RAM location. In the example in Figure

scratchpad_transfers:

STORE sX, 04 ; Write register sX to RAM location 04

FETCH sX, 04 ; Read RAM location 04 into register sX

Figure 5-1: Directly Addressing Scratchpad RAM Locations

Indirect Addressing

Using indirect address, the actual RAM address is the value contained in a specified register. Whereas direct addressing requires the RAM address to be known before assembly, indirect addressing provides additional program flexibility. The application code can compute or modify the RAM address based on other program data. The code in Figure

PicoBlaze | www.xilinx.com | 45 |

UG129 (v1.1.2) June 24, 2008