R

Chapter 3: PicoBlaze Instruction Set

|

|

|

|

| 18x18 Multiplier |

|

|

|

|

| A[17:8] |

1 | PicoBlaze Microcontroller |

|

| A[7:0] | |

|

|

|

| ||

| IN_PORT[7:0] | OUT_PORT[7:0] |

| EN | P[15:8] |

|

|

| |||

0 | SEL | PORT_ID[7:0] | [0] |

| P[7:0] |

| READ_STROBE |

|

| ||

|

|

| B[17:8] | ||

|

|

|

| ||

|

|

|

|

| |

|

| WRITE_STROBE |

|

|

|

|

|

|

|

| B[7:0] |

|

|

|

| EN |

|

|

|

|

|

| UG129_c3_02_052004 |

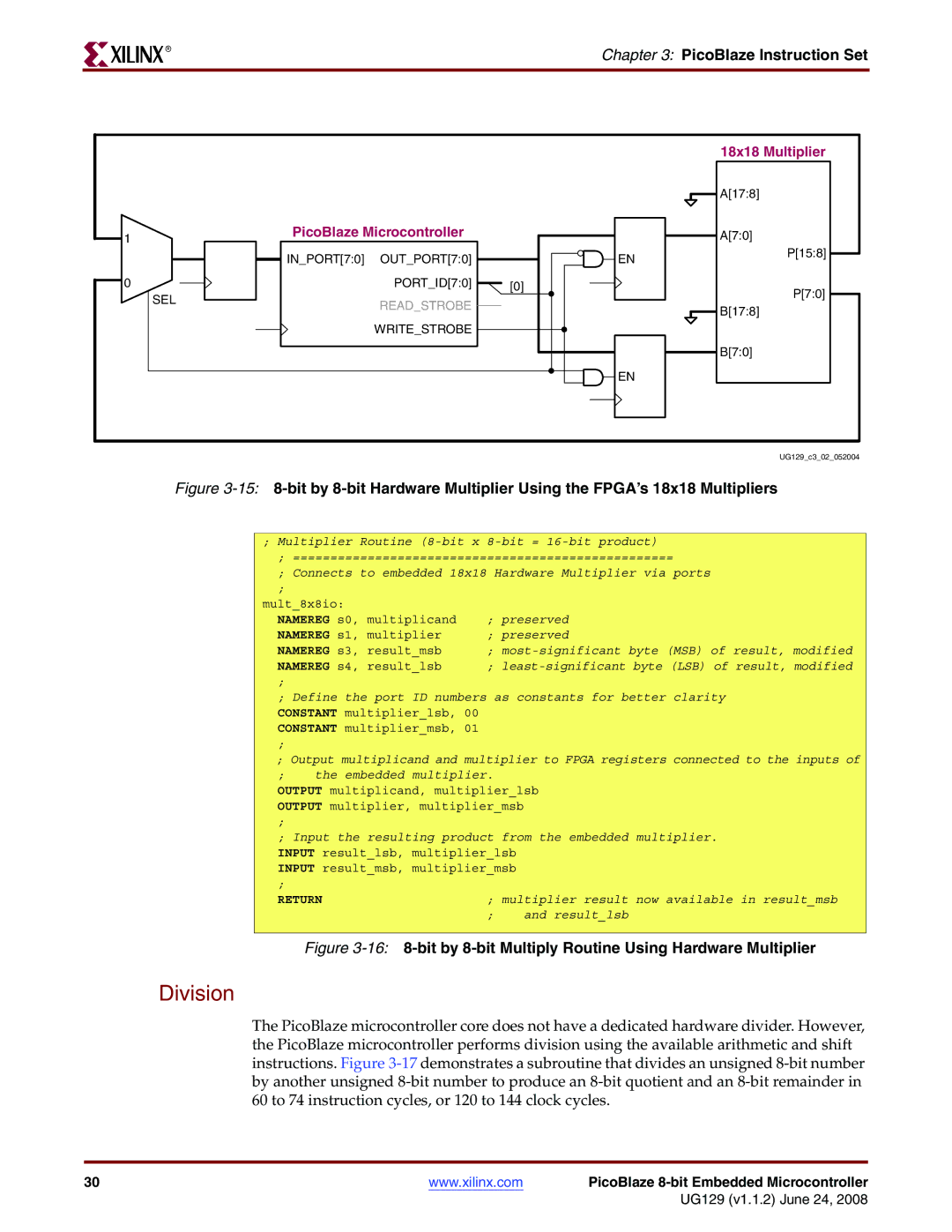

Figure 3-15: 8-bit by 8-bit Hardware Multiplier Using the FPGA’s 18x18 Multipliers

;Multiplier Routine

;===================================================

;Connects to embedded 18x18 Hardware Multiplier via ports

; |

|

mult_8x8io: |

|

NAMEREG s0, multiplicand | ; preserved |

NAMEREG s1, multiplier | ; preserved |

NAMEREG s3, result_msb | ; |

NAMEREG s4, result_lsb | ; |

; |

|

; Define | the port ID numbers as constants for better clarity | |

CONSTANT | multiplier_lsb, | 00 |

CONSTANT | multiplier_msb, | 01 |

; |

|

|

;Output multiplicand and multiplier to FPGA registers connected to the inputs of

;the embedded multiplier.

OUTPUT multiplicand, multiplier_lsb

OUTPUT multiplier, multiplier_msb

;

; Input the resulting product from the embedded multiplier. INPUT result_lsb, multiplier_lsb

INPUT result_msb, multiplier_msb

; |

|

|

|

RETURN | ; | multiplier result | now available in result_msb |

| ; | and result_lsb |

|

Figure 3-16: 8-bit by 8-bit Multiply Routine Using Hardware Multiplier

Division

The PicoBlaze microcontroller core does not have a dedicated hardware divider. However, the PicoBlaze microcontroller performs division using the available arithmetic and shift instructions. Figure

30 | www.xilinx.com | PicoBlaze |

UG129 (v1.1.2) June 24, 2008