UG129 v1.1.2 June 24

PicoBlaze 8-bit Embedded Microcontroller User Guide

Version Revision

Revision History

Technical Support Limitations

Limited Warranty and Disclaimer

Limitations

Limitation of Liability

Preface Acknowledgments

Acknowledgments

About This Guide

Guide Contents

Preface About This Guide

Table of Contents

Interrupts

Performance

Appendix C PicoBlaze Instruction Set and Event Reference

Introduction

PicoBlaze Microcontroller Features

Introduction

PicoBlaze Microcontroller Functional Blocks

General-Purpose Registers

Instruction Program Store

Input/Output

Arithmetic Logic Unit ALU

Flags

Byte Scratchpad RAM

CALL/RETURN Stack

Reset

Program Counter PC

Program Flow Control

Why the PicoBlaze Microcontroller?

Why Use a Microcontroller within an FPGA?

Why the PicoBlaze Microcontroller?

Weaknesses

Strengths

PicoBlaze Interface Signals

PicoBlaze Interface Signal Descriptions

Signal Direction Description

Readstrobe

1PicoBlaze Instruction Set alphabetical listing

PicoBlaze Instruction Set

Enable Interrupt

Returni Disable

Address Spaces

Instruction 1Kx18 Direct

Processing Data

Logic Instructions

PicoBlaze Instruction Set

3Inverting an Individual Bit Location

2Complementing a Register Value

Arithmetic Instructions

616-Setting a Bit Location

SUB and Subcy Subtract Instructions

10Incrementing and Decrementing a Register

Multiplication

148-bit by 8-bit Multiply Routine Produces a 16-bit Product

Division

168-bit by 8-bit Multiply Routine Using Hardware Multiplier

18Loading a Register with Itself Acts as a NOP Instruction

No Operation NOP

Test and Compare

Setting and Clearing Carry Flag

22The Test Instruction Affects the Zero Flag

Shift and Rotate Instructions

25Generate Parity for a Register Using the Test Instruction

5PicoBlaze Rotate Instructions Rotate Left Rotate Right

SRX

Program Flow Control

Moving Data

6Instruction Conditional Execution Description

Program Flow Control

CALL/RETURN

Program Flow Control

UG129 v1.1.2 June 24

1Simple Interrupt Logic

Interrupts

2Example Interrupt Flow

Example Interrupt Flow

Example Interrupt Flow

3Interrupt Timing Diagram

Interrupts

Indirect Addressing

Scratchpad RAM

Address Modes

Direct Addressing

Scratchpad RAM

Implementing a Look-Up Table

Stack Operations

Fifo Operations

Stack Operations

Scratchpad RAM

Portid Port

Input and Output Ports

1INPUT Operation and Fpga Interface Logic

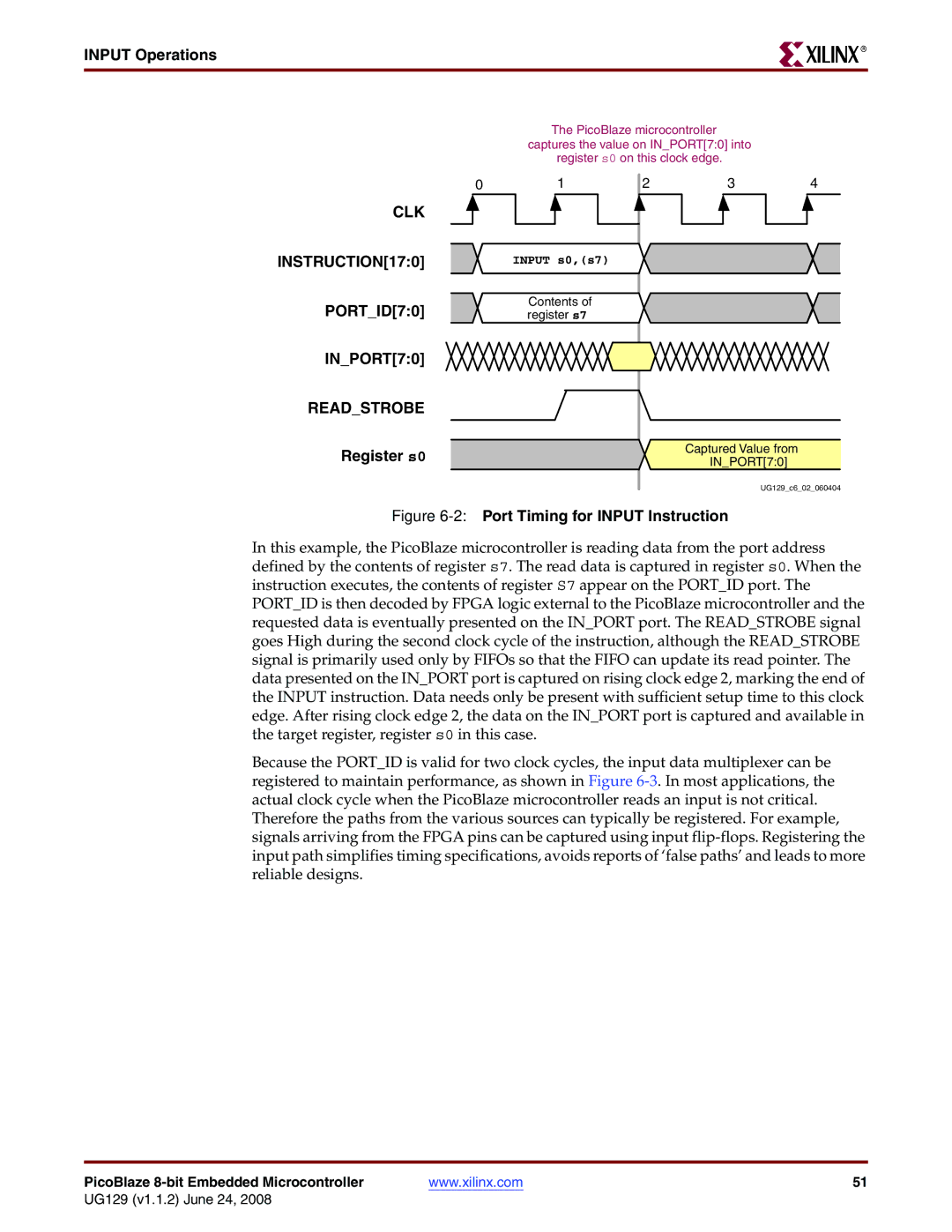

Input Operations

Register s0

Input Operations

PORTID70

INPORT70

Applications with Few Input Sources

Readstrobe Interaction with FIFOs

Input and Output Ports

Output Operations

Output Operations

Fpga Register

Simple Output Structure for Few Output Destinations

8Use Constant Directives to Declare Output Port Addresses

9Pipelining the Portid Decoding Improves Performance

Pipelining for Maximum Performance

Pipelining for Maximum Performance

Effective Pipelining Improves Read Performance

Repartitioning the Design for Maximum Performance

Standard Configuration Single 1Kx18 Block RAM

Instruction Storage Configurations

Two PicoBlaze Microcontrollers Share a 1Kx18 Code Image

Instruction Storage Configurations

Distributed ROM Instead of Block RAM

6Using Distributed ROM for Instruction Memory

Instruction Storage Configurations

Frequency

Performance

Input Clock Frequency

Predicting Executing Performance

Performance

Assembler

PicoBlaze Development Tools

Assembly Errors

Input and Output Files

PicoBlaze Development Tools

Mediatronix pBlazIDE

Configuring pBlazIDE for the PicoBlaze Microcontroller

4Example of How Kcpsm Source Code Converts to pBlazIDE Code

Importing KCPSM3 Code into pBlazIDE

Function KCPSM3 Directive PBlazIDE Directive

Differences Between the KCPSM3 Assembler and pBlazIDE

Directives

Differences Between the KCPSM3 Assembler and pBlazIDE

PicoBlaze Development Tools

Using the PicoBlaze Microcontroller in an Fpga Design

Vhdl Design Flow

KCPSM3 Module

Using the PicoBlaze Microcontroller in an Fpga Design

Connecting the Program ROM

Black Box Instantiation of KCPSM3 using KCPSM3.ngc

Black Box Instantiation of KCPSM3 using KCPSM3.ngc

Generating the Program ROM using progrom.coe

Generating an ESC Schematic Symbol

Using the PicoBlaze Microcontroller in an Fpga Design

Assembler Directives

Locating Code at a Specific Address

Naming or Aliasing Registers

PBlazIDE

Defining Constants

Naming the Program ROM Output File

Defining I/O Ports pBlazIDE

Input Ports

Output Ports

Defining I/O Ports pBlazIDE

5Example of pBlazIDE Dsout Directive

Input/Output Ports

Custom Instruction Op-Codes

Custom Instruction Op-Codes

Assembler Directives

Simulating PicoBlaze Code

Instruction Set Simulation with pBlazIDE

Edit

Simulator Control Buttons

Instruction Set Simulation with pBlazIDE

2pBlazIDE Simulator Control Buttons Function Assemble

Pause

Run

Step Over

Run to Cursor

Turbocharging Simulation using FPGAs

Turbocharging Simulation using FPGAs

Simulating PicoBlaze Code

Related Materials and References

Chapter Related Materials and References

KCPSM3 Syntax

Example Program Templates

Appendix Example Program Templates

PBlazIDE Syntax

ADD sX, Operand -Add Operand to Register sX

PicoBlaze Instruction Set and Event Reference

Appendix PicoBlaze Instruction Set and Event Reference

Addcy sX, Operand -Add Operand to Register sX with Carry

SX, Operand Logical Bitwise and Register sX with Operand

SX, Operand Logical Bitwise and Register sX with Operand

Examples

Table C-1CALL Instruction Conditions Description

Condition

Figure C-4COMPARE Operation

Compare sX, Operand Compare Operand with Register sX

Disable Interrupt Disable External Interrupt Input

Enable Interrupt Enable External Interrupt Input

Disable Interrupt Disable External Interrupt Input

KCPSM3 Instruction PBlazIDE Instruction

Figure C-5FETCH Operation

Portid Å Operand SX Å Inport PC Å PC +

Interrupt Event, When Enabled

Table C-2JUMP Instruction Conditions Description

Load sX, Operand Load Register sX with Operand

Or sX, Operand Logical Bitwise or Register sX with Operand

Or sX, Operand Logical Bitwise or Register sX with Operand

Figure C-7OUTPUT Operation and Fpga Interface Logic

Reset Event

Reset Event

Table C-3PicoBlaze Reset Values Resource Reset Event Effect

Table C-4RETURN Instruction Conditions Description

PBlazIDE Equivalent RET, RET C, RET NC, RET Z, RET NZ

Table C-6Rotate Right RR Operation

RL sX Rotate Left Register sX

RR sX Rotate Right Register sX

Table C-5Rotate Left RL Operation

SL 0 1 X a sX Shift Left Register sX

SL 0 1 X a sX Shift Left Register sX

Table C-7Shift Left Operations

SR 0 1 X a sX Shift Right Register sX

Shift Right with ‘ 0’ fill

Figure C-8STORE Operation

Store sX, sY

SUB sX, Operand -Subtract Operand from Register sX

Figure C-10SUBCY Instruction

Registers sX Flags CARRY, Zero PBlazIDE Equivalent Subc

Figure C-11ZERO Flag Logic for Test Instruction

PicoBlaze 8-bit Embedded Microcontroller 117

XOR sX, Operand Logical Bitwise XOR Register sX with Operand

Table D-1PicoBlaze Instruction Codes

Instruction Codes

Jump Z

PicoBlaze 8-bit Embedded Microcontroller 121

Appendix Instruction Codes

Register and Scratchpad RAM Planning Worksheets

Registers

Reg Description

Scratchpad RAM

Appendix Register and Scratchpad RAM Planning Worksheets

Loc Description