Networking Silicon — 82555

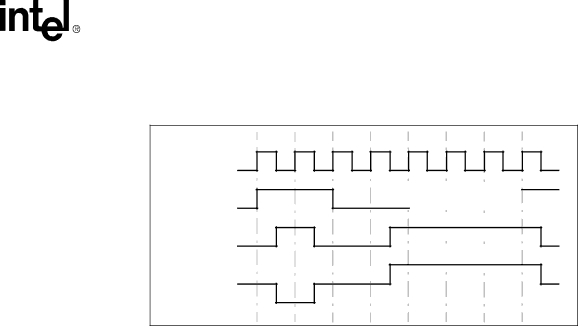

maintained (either positive, negative or zero). When an NRZ “1” arrives at the input of the encoder, the output steps to the next level. The order of steps is

Clock

NRZ

NRZ1

1

1

1

1

1

1

0 0

00

0![]() 0

0

1 |

| 0 |

| 0 |

|

|

|

| |

1 |

| 0 |

| 0 |

|

| |||

|

| |||

|

|

|

| |

|

|

|

|

|

1 | 0 | 0 | ||

1

1

1

Figure 6. NRZ to MLT-3 Encoding Diagram

4.2.3100BASE-TX Transmit Framing

The 82555 does not differentiate between the fields of the MAC frame containing preamble, start of frame delimiter, data and Cyclic Redundancy Check (CRC). When TXEN is asserted, the 82555 accepts data on the MII TXD[3:0] lines, encodes it, and sends it out onto the wire. The 82555 encodes the first byte of the preamble as the “JK” symbol, encodes all other pieces of data according to the 4B/5B lookup table, and adds the “TR” code after the end of the packet (de- assertion of TXEN). The 82555 scrambles and serializes the data into a 125 Mbps stream, encodes it as

Datasheet | 15 |