MITX-430/MITX-440-DVI-2E

Contact Address

Contents

Contents

Operation

OEM-Reserved Status Code Ranges

List of Tables

List of Tables

Table A-1

List of Tables

List of Figures

List of Figures

About this Manual

Overview of Contents

Abbreviations

About this Manual

GBE

PWM

Notation Description

Conventions

Bold

Summary of Changes

Comments and Suggestions

About this Manual About this Manual

Part Number Publication Date Description

About this Manual

About this Manual

Features

Single Core Processor Board Features

Function Features

Introduction

Introduction

USB

Dual Core Processor Board Features

MITX-440-DVI-2E

Introduction

Standard Compliances

Standard Compliances

Standard Description

Declaration of Conformity

Board Accessories

Mechanical Data

Ordering Information

Supported Board Models

Product Identification

Dual Core Processor Board -Serial Number Location

Introduction

Hardware Preparation and Installation

Environmental and Power Requirements

Environmental Requirements

Environmental Requirements

Hardware Preparation and Installation

Critical Temperature Spots

Maximum Allowable Temperature 0C

Thermal Requirements

Power Requirements Single Core Processor Board

Full Loading Running Burn-in Test

Idle Mode Power Consumption

Power Requirements Dual Core Processor Board

VGA and Lvds dual display, without DVI display

Board Thermal Management and Placement

Board Thermal Management

Board Thermal Management

Unpacking and Inspecting the Board

Shipment Inspection

Preparing the Installation Environment

Environmental Damage

Processor Cooler Installation and Removal

Installing the Processor Cooler

Memory Module Installation and Removal

Removing Memory Module

Hardware Preparation and Installation

Controls, LEDs, and Connectors

Board Layout

Controls, LEDs, and Connectors

Dual Core Motherboard Components

Connectors

Clear Cmos P3

Lvds Header J5

Clear Cmos

Lvds Backlight Header P23

Lvds Power

Mini IDE Header J8

USB Flash Header P10

USB Flash Header Pin Definition

USB Header P12

ELO Touch Screen Header P6

USB Header Pin Definition

ELO Touch Screen Header Pin Definition

COM Header P9, P27

Gpio Header P4

11 RS-232/422/485 P18

Power COM P8, P26

12 RS-232/422/485 Jumper Selection P28

13 COM4, COM5 Header Pin Definition

14 COM4, COM5 Pin9 Selection

TPM Header P2

15 TPM Header Pin Definition

LPT Header P11

Front Panel Header P15

16 LPT Header Pin Definition

17 Front Panel Header Pin Definition

Bios Program Header P16

18 Bios Program Header Pin Definition

Fan Header P1, P13

19 Smart Fan Header Pin Definition

20 Mini Pcie Wireless LAN LED Header Pin Definition

Mini Pcie LED P14

Case Open Header P25

21 Case Open Header Pin Definition

Block Diagram

Functional Description

SMBus Interface and Devices

Pineview-D Processor

Functional Description

Board I2C Device Connection

System Memory

Ethernet Interfaces

PCI-E Port

I2C Device Address

USB Interface

PCI-E Connection

VGA, LVDS, LPC, and Audio Interface

USB Ports Connection

Bios Device

Gpio Configuration

DVI Interface

11 IDE

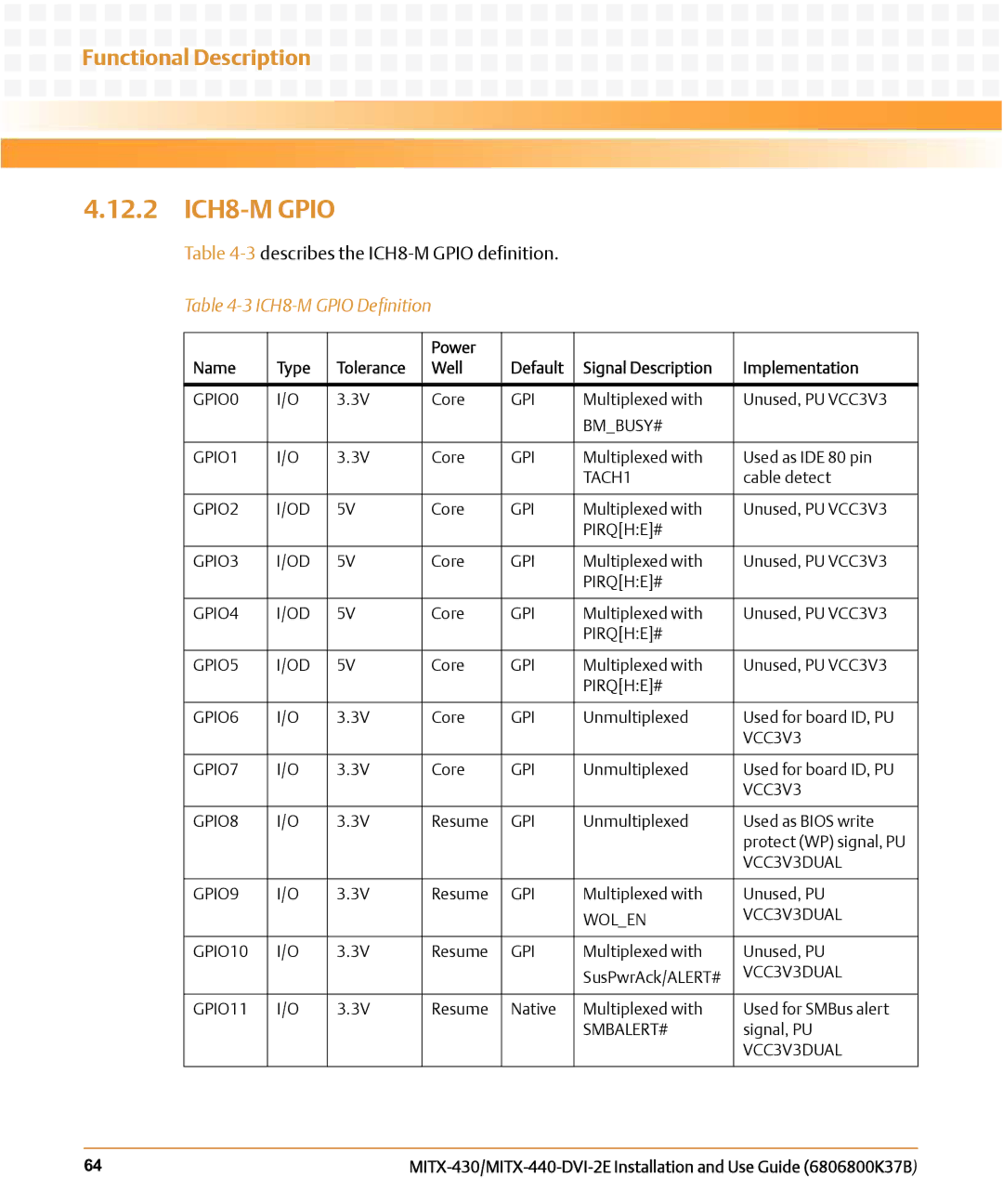

12.2 ICH8-M Gpio

ICH8-M Gpio Definition

GPIO12

Power Name Type

Well Default Signal Description Implementation

GPIO36

Chipset

Video

Clock Generator

Storage

HW Monitor

Super I/O

SPI Flash

Watchdog Timer

Power Management

Debug

Manageability

Functional Description

Boot Process

Initiating Setup

Operation

Post

Setup Utility

Setup Utility

Main Menu

Operation

Legacy Oprom Support

Advanced Menu

Advanced Menu

Acpi Settings

Trusted Computing

S5 RTC Wake Setting

CPU Configuration

IDE Configuration

Execute Disable Bit

10 IGD-LCD Control

CRT LFP DVI CRT +LFP CRT +DVI

11 USB Configuration

Ehci Hand-off

13 Super IO Configuration

12 EMC2103 H/W Monitor

14 Serial Port 1 Configuration

15 Serial Port 2 Configuration

16 Serial Port 3 Configuration

17 Serial Port 4 Configuration

18 Serial Port 5 Configuration

19 Serial Port 6 Configuration

20 Parallel Port Configuration

21 Watchdog Timer Configuration

22 W83627UHG H/W Monitor

23 Serial Port Console Redirection

24 COM1 and COM2 Console Redirection Settings

Bits per second

Chipset Menu

25 Chipset Menu

26 Host Bridge

27 South Bridge

Boot Menu

28 Boot Menu

Security Menu

Save & Exit Menu

29 Security Menu

30 Save & Exit Menu

Post Codes

Status Code Ranges

31 Status Code Ranges

Status Code Range Description

Standard Status Codes

SEC Status Codes

32 SEC Status Codes

Status Code Description

Operation PEI Status Codes

33 PEI Status Codes

0x36

S3 Resume Progress Codes

34 PEI Beep Codes

PEI Beep Codes

# of Beeps Description

Operation DXE Status Codes

35 DXE Status Codes

Operation

Operation

DXE Beep Codes

CPU Exception Status Codes

36 DXE Beep Codes

37 CPU Exception Status Codes

ASL Status Codes

38 ASL Status Codes

OEM-Reserved Status Code Ranges

39 OEM-Reserved Status Code Ranges

Operation

Operating System and Driver Support

Supported Operating System

Supported Drivers

Supported Drivers

Operating System and Driver Support

Related Specifications

Table A-2 Related Specifications

ARelated Documentation

Emerson Embedded Communications Computing Documents

Related Documentation

108

Safety Notes

Safety Notes

EMC

Installation

Vcci

Safety Notes

Safety Notes

Operation

System Overheating Cooling Vents

Safety Notes

Safety Notes

Configuration Switches/Jumpers

Personal Injury or Short Circuits Blade or Power Supply

Grounding

Connectors and Cabling

Safety Notes

PEM

Safety Notes

Fans/Blowers

Safety Notes

Expansion and FRU Replacement

Safety Notes

Hot Swap

System Damage If the system is overloaded it gets damaged

PMC Modules

SFP/SFP+ Modules

Battery

Laser

Safety Notes

Environment

Safety Notes

Sicherheitshinweise

Sicherheitshinweise

System Installation

Sicherheitshinweise

Sicherheitshinweise

Betrieb

Überhitzung des Systems Lüftungsöffnungen

Sicherheitshinweise

Sicherheitshinweise

Verletzungen oder Kurzschlüsse Blade oder Stromversorgung

Schaltereinstellungen

Erdung

Stecker und Verkabelung

Sicherheitshinweise

PEM

Sicherheitshinweise

Lüfter

Beschädigung der Lüfter

Erweiterung und FRU Austausch

Sicherheitshinweise

Hot Swap

PMC Module

Fehlfunktion des Produktes und/oder Verletzungsgefahr

Batterie

Sicherheitshinweise

Umweltschutz

Index

Index

Page

HOW to Reach Literature and Technical Support

Embedded Computing

Functional Description

Functional Description