Functional Description

Functional Description

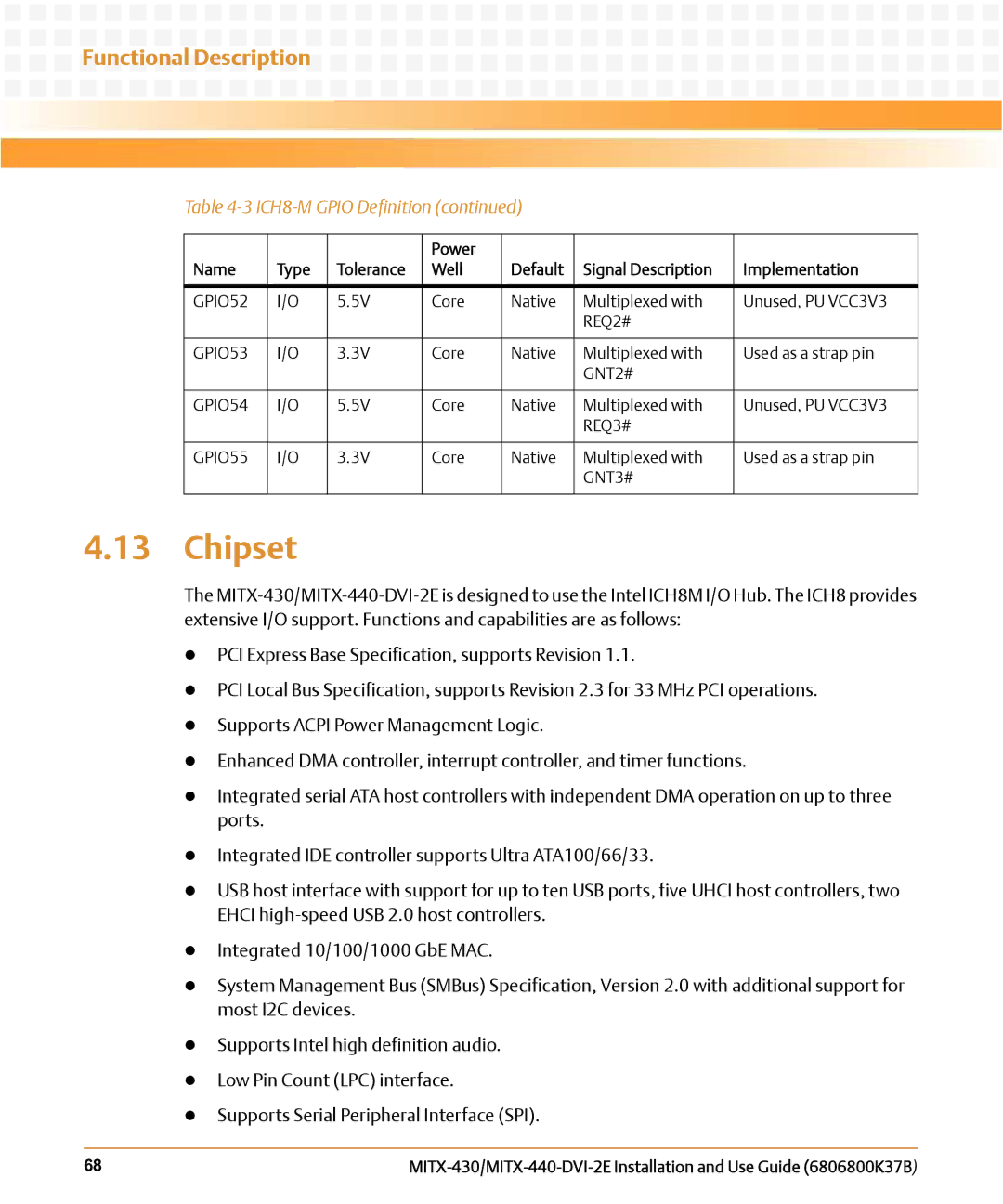

Table 4-3 ICH8-M GPIO Definition (continued)

|

|

| Power |

|

|

|

Name | Type | Tolerance | Well | Default | Signal Description | Implementation |

|

|

|

|

|

|

|

GPIO52 | I/O | 5.5V | Core | Native | Multiplexed with | Unused, PU VCC3V3 |

|

|

|

|

| REQ2# |

|

|

|

|

|

|

|

|

GPIO53 | I/O | 3.3V | Core | Native | Multiplexed with | Used as a strap pin |

|

|

|

|

| GNT2# |

|

|

|

|

|

|

|

|

GPIO54 | I/O | 5.5V | Core | Native | Multiplexed with | Unused, PU VCC3V3 |

|

|

|

|

| REQ3# |

|

|

|

|

|

|

|

|

GPIO55 | I/O | 3.3V | Core | Native | Multiplexed with | Used as a strap pin |

|

|

|

|

| GNT3# |

|

|

|

|

|

|

|

|

4.13Chipset

The

zPCI Express Base Specification, supports Revision 1.1.

zPCI Local Bus Specification, supports Revision 2.3 for 33 MHz PCI operations.

zSupports ACPI Power Management Logic.

zEnhanced DMA controller, interrupt controller, and timer functions.

zIntegrated serial ATA host controllers with independent DMA operation on up to three ports.

zIntegrated IDE controller supports Ultra ATA100/66/33.

zUSB host interface with support for up to ten USB ports, five UHCI host controllers, two EHCI

zIntegrated 10/100/1000 GbE MAC.

zSystem Management Bus (SMBus) Specification, Version 2.0 with additional support for most I2C devices.

zSupports Intel high definition audio.

zLow Pin Count (LPC) interface.

zSupports Serial Peripheral Interface (SPI).

68 |