2635A

Limited Warranty & Limitation of Liability

Table of Contents

2635A

Front Panel Operations

Memory Card Operations

Printer Operations

Index

2635A

List of Tables

Viii

List of Figures

Overall PC-to-Instrument Modem Connection

Interference Information

Safety Terms in this Manual

Symbols Marked on Equipment

AC Power Source

DC Power Source

Use the Proper Power Cord

Use the Proper Fuse

Ten Minute Tour

Introduction

Power Func

SET Func

OFF VAC

Ten Minute Tour

Selecting a Measurement Scale. Select

Scan

Scan MON

SET

Review

SLO

Alrm

Mx+B SET Mx+B

YEAR TotAL

OFF

LISt

DESt

Mode

ALL

Xxiii

Xxiv

Preparation for Use

2635A

Preparation for Use 1 Introduction

Hydra

Introduction

Operating Modes

Data Bucket Features

Ground Terminal AC Power Connector Universal Input Module

Alarm Outputs Connector Digital I/O Connector RS-232C

Front Panel Operation

Memory Card Operation

Modem Operation

Computer Operation

Printer Operation

Measurement Capabilities

Applications Software

Options and Accessories

Connector Set, 2620A-100

Hydra Starter Package

Hydra Logger

Setting Up the Instrument

Options and Accessories

Unpacking and Inspecting the Instrument

Model

Adjusting the Handle

Connecting the Instrument to a Power Source

Input Channels

AC Operation

DC Operation

Using Shielded Wiring

Measurement Connections

Crosstalk

Universal Input Module Connections

Measurement Connections

Wire 2T Connection Source

Wire 4T Connection Source

Sense

Resistance

Alarm Outputs Connections

DC Power

Alarm Outputs

External Trigger Input

Digital I/O Connections

Digital I/O

Totalizer Input

Digital I/O

Controls and Indicators

Front Panel Indicators

Front Panel Controls

Auto MON

11. Secondary Display

12. Annunciator Display

Front Panel Keys Description

Rate K J Clock K I Mode K P

Key

Func Alarm

Clear Local K Comm K L Zero Single K Q

Annunciator Descriptions

MON Scan SET

Annunciator Annunciator Descriptions

OFF Auto Limit HI, LO Review MIN, MAX Last PRN EXT REM CAL

2635A

Front Panel Operations

Using the Monitor Mode Using the Review Mode

Front Panel Operations

Hydra Data Bucket

How to use the Control/Annunciator Diagrams

Summary of Front Panel Operations

Configuring the Instrument for Operation

Turning the Power on

Configuration Reset Default Settings Parameter

Default Setting

Selftest Error Codes Description

Code

Restrictions

Configuring a Measurement Channel

Selecting a Channel

Configuring a Channel to Measure DC Volts

Func SET Func

Configuring a Channel to Measure AC Volts

Configuring a Channel to Measure AC Volts

Configuring a Channel to Measure Resistance

Configuring a Channel to Measure Resistance

Configuring a Channel to Measure Frequency

Configuring a Channel to Measure Frequency

Configuring a Channel to Measure Temperature

Resistance-Temperature Detectors

Resistance Temperature Detectors Restrictions

Thermocouples

Thermocouple Ranges Type Material

Positive Lead Color

ANSI* IEC

Negative Lead Material

Configuring a Channel to Measure Temperature RTDs

Setting Operating Conditions

Configuring a Channel Off

Setting the Scan Interval

11. Setting the Scan Interval

Setting the Measurement Rate

Setting the Alarms

Alarm Indications While Scanning

RAtE

Clearing Alarm Parameters from a Channel

Alarm Indications While Monitoring

Alarm Indications While Reviewing

Alarms and Autoprinting

Alarms and Monitor-Alarm Triggering

Alarms and Mx+B Scaling

TLL Alarm Outputs Channels 0 to Decimal

TTL Alarm Outputs Channels 4 to

Channels

13. Setting the Alarms

Alrm Limit

Clearing Mx+B Scaling from a Channel

Setting the Mx+B Scaling

Examples

14. Setting the Mx+B Scaling

Required From the previous

Using the Scan Mode

Memory Card Data Extraction

Path to OPEn DAtxx Menu

Memory Card Error Messages

16. Memory Card Error Messages

Using the Monitor Mode

17. Using the Monitor Mode

Using the Review Mode

18. Using the Review Mode

Additional Features

Monitor-Alarm Trigger

Scan Triggering Options

External Trigger

Totalizer Operation

19. Scan Triggering Options

Digital Input/output Lines

Xxxxx

Mn.dY

Setting Date and Time

Year

Returning to the Local Mode. Press

Returning to the Local Mode

Reading Instrument Software Versions

REM Monitor Mode Review

Instrument Interfaces

Front Panel Key Lockout Options

Memory Card Interface

RS-232 Computer Interface

Using the RS-232 Computer Interface With a Printer

Using the RS-232 Computer Interface With a Modem

2635A

Memory Card Operations

Recording Measurement Results During Scanning

256KB

Insertion Direction PIN Connector

WRITE-PROTECT Switch

Lithium Battery 3 Volts

Summary of Memory Card Operations

Memory Card Capacity

Setup Files

Data Files

Installing or Replacing the Memory Card Battery

Inserting and Removing the Memory Card

Error

Memory Card Error Codes Probable Cause

Initializing a Memory Card

Files

Init

SUrE

Recording Measurement Results During Scanning

MOdE

Setup File Procedures

Using Setup Store

SEtUP

StorE

Using Setup Load

Using Setup Load to Load Configuration Files

Using Setup Erase

ErASE

DAtA

Data File Procedures

Using Data Open

Using Data Erase

Using Data Erase to Delete a Measurement Data File

Setup and Data Files Directory

NnnnK

Setup and Data File Current Status

USEd

Memory Card File Operations to and from a PC

Computer Operations

Op82f.eps

Connecting the Instrument to a PC

Summary of Computer Operations

PC Connection With DB-25

Connector

PC Connection With DB-9

Configuring the Instrument for Computer Operations

PAR

Configuring the PC for Computer Operations

Testing the Instrument/PC RS-232 Interface

Rstfunc 0,VDC,4PRINTTYPE 0,0PRINT 1*TRG

2635A

Testing the RS-232 Interface Using Gwbasic

Open COM1,9600,N,8,1,CS,CD for Random AS #1

Testing the RS-232 Interface Using Qbasic

Print #1, Printtype 0,0PRINT INPUT$20, #1

IDN?

Input Terminators

Computer Interface Commands and Operation

How the Instrument Processes Input

How the Instrument Processes Output

Input String Examples

Sending Numeric Values to the Instrument

Status Registers

Instrument Event Register IER

Overview of Status and Event Data Registers

Instrument Event Register IER Description

Standard Event Status Register ESR

Bit Name

Status Byte Register STB

Bit Event Status Register ESR Name Description

Computer Interface Command Set

Xmodem File Transfers

IEB

MAV ESB

Command and Query Summary

Echo

DIOLEVELS? Dolevel

Func FUNC? RTDR0 RTDR0? RANGE?

Rate RATE?

MAX? MIN? NEXT?

MON MONCHAN? MONVAL?

Scalemb SCALEMB?

Tempconfig TEMPCONFIG?

Lock LOCK? Locs Lwls Rems Rwls

Format FORMAT?

Reviewclr

IDN? TST?

Date Time TIMEDATE?

Total TOTAL? Totaldbnc TOTALDBNC?

Trigger TRIGGER?

Command and Query Reference

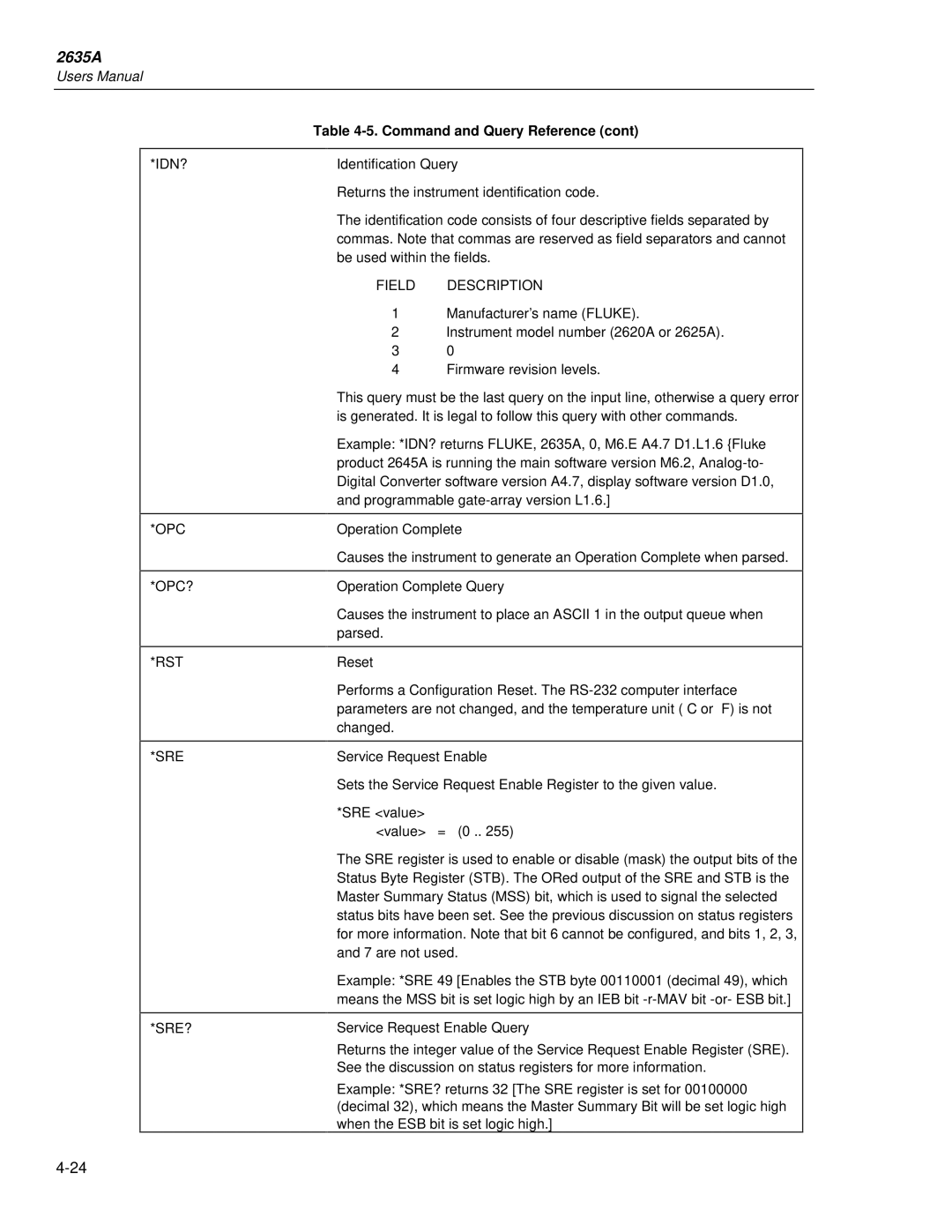

Cntlc CLS ESE ESE? ESR?

OPC OPC? RST SRE SRE?

IDN?

Field Description

TRG

TST? WAI

ALARMS?

Alarmassoc

ALARMASSOC?

Alarmassocclr

Alarmdolevel

ALARMDOLEVELS?

LO OFF

Alarmlimit

ALARMLIMIT? CLS Date

DIOLEVELS? Digital I/O State Query

DIR

Echo ESE ESE? ESR? FILEERROR? Fileload

FILEOPEN? Fileremove

FILESPACE? Filestore

Configuration File Tag

Format

Measurement Units String

MX+B

VDC

Func

Range Voltage Ohms Frequency

FUNC? IDN? IEE

IEE? IER?

Intvl INTVL? LAST?

Lock

LOCK? Locs LOG? LOGGED?

LOGBIN? Logclr LOGCLR1 LOGCOUNT?

Logmode LOGMODE? Lwls

MAX?

BIT Memory Card Battery Status

MAX? MCARD?

Mcardformat

MCARDSIZE?

Disables monitoring

OPC OPC? Print

PRINT? Printtype

PRINTTYPE?

Rate RATE? Rems Reviewclr RST RTDR0

RTDR0? Rwls

Scalemb

SCALEMB? Scan

SCAN? SCANTIME? SRE SRE? STB? Tempconfig

TEMPCONFIG?

Total

TOTAL? Totaldbnc TOTALDBNC? TRG Trigger

Returns an integer representing the present trigger type

Sample Program Gwbasic 1

Sample Program Gwbasic 2

Sample Program Qbasic 1

Sample Program QBASIC2

Sample Program Qbasic 3

Sample Program QuickC 1of

Sample Program QuickC 2

Sample Program QuickC 3

Sample Program QuickC4

Sample Program QuickC5

Printer Operations

Op83f.eps

Connecting the Instrument to a Printer

Summary of Printer Operations

PARALLEL-INPUT

SERIAL-INPUT

Printer

Configuring for Printer Operations

Configuring the RS-232 Ports for Print Operations

Printing Measurement Results During Scanning

Problems?

Printing Measurement Data and Memory Card Directory

Printing Measurement Data and Memory Card Directory

Printing the Review Array

Printing the Review Array

Printing the Directory of the Memory Card

Printing the Memory Card Directory

2635A

Configuring the Instrument for Modem Operations

Modem Operations

Op84f.eps

Summary of Modem Operations

Overall PC-to-Instrument Modem Connection

Connecting the Modem to a PC for Modem Configuration

Configuring the Instrument Modem for Modem Operations

Modem Connection With PC DB-9 Connector

Modem Connection With PC DB-25 Connector

Connecting the Modem to an Instrument

Connecting the Modem to an Instrument

Configuring the Instrument for Modem Operations

Enter

Testing the RS-232/Modem Interface

Maintenance

Dedicated Alarm Output Test

Calibrator

Introduction Cleaning

Line Fuse

Performance Tests

Selftest Diagnostics and Error Codes

Error Power-Up Error Codes Description

Performance Tests

Recommended Test Equipment Minimum Specification

Instrument Type

Recommended Model

Instrument Type Recommended Model

Accuracy Verification Test

Function

Range

Input Level Frequency

Channel Integrity Test

Thermocouple Measurement Range Accuracy Test

Thermocouple Temperature Accuracy Test

Four-Terminal Resistance Test

Open Thermocouple Response Test

UUT

Hydra Input Module

5700A

RTD Temperature Accuracy Test

RTD Temperature Accuracy Test Using Decade Resistance Source

RTD Temperature Accuracy Test Using DIN/IEC 751 RTD

Temperature Simulated

Temperature Accuracy

Decade Resistance Source

Digital Input/Output Verification Tests

Digital Output Test

Dolevel 0,0 CR

Digital Input Test

Totalizer Test

Terminal Grounded

Digital Input Values

State of Digital Inputs

Dedicated Alarm Output Test

Totalizer Sensitivity Test

Maintenance

Alarm Output

GND Source Input

Module Sense

Hydra

Calibration

External Trigger Input Test

Service

Variations in the Display

Appendices

Appendix Title

Page

Specifications

Accuracies at Ambient Temperatures Other than Specified

Resolution

DC Voltage Measurements

Normal Mode Rejection

Common Mode Rejection

Accuracy

Input Impedance

Cross-Talk Rejection

Appendices

Maximum Input

Resolution

Accuracy

Temperature Measurements Thermocouples

Type Temperature Days Year Slow Fast 0C to 60C

2635A

Temperature Measurements RTDs

Common Mode and Normal Mode Rejection

Open Thermocouple Detect

RTD

Wire Accuracy

Temperature Slow Fast

AC Voltage Measurements

RTD Type

Minimum Input for Rated Accuracy

Table A-10. AC Voltage Measurements Resolution Range

Resolution Slow Fast

Crest Factor Error

DC Component Error

2635A Maximum Voltage Input VS. Frequency Input

Maximum Crest Factor

Resistance Measurements

2635A Wire Accuracy

Resolution and Accuracy

Frequency Measurements

Input Sensitivity

Typical Scanning Rate

Table A-17. Typical Scanning Rate

Digital Inputs

Maximum Autoranging Time

Totalizing Input

Trigger Inputs

Input Voltages

Minimum Pulse Width Maximum Frequency Specified Conditions

Maximum Latency

Real-Time Clock and Calendar

Digital and Alarm Outputs

Environmental Specifications

General

Weight

Power

2635A Voltage Ratings

Size

AC Signal Cross Talk in a DC Voltage Channel

Crosstalk Considerations

AC Signal Cross Talk into an AC Voltage Channel

AC Signal Cross Talk into an Ohms Channel

AC Signal Cross Talk into a Frequency Channel

AC Signal Crosstalk into a Temperature Channel

2635A

Binary Upload of Logged Data

Decoding the Ascii String

+--------+--------+--------+--------+

Figure C-1. Ascii String Decoding

Floating Point Conversion

Mlsb Lmsb

Sign Bit

Mmsb

Figure C-2. FloatingPoint Conversion

Example

Figure C-3. Example

RS-232 Cabling

Cables

Figure D-1. Summary of RS-232 Connections

RS-232 Cabling D

Figure D-3. Hydra DB-9 to PC DB-25 RS-232 Connection

RS41 Cable or Equal

Printer

Side

Connector

Side Male Female

2635A

Bit Binary-Coded-Decimal Table

Table E-1 -Bit Binary-Coded-Decimal

Binary

Data File Format

Setup File Format

Memory Card File Formats

Trigger

Memory Card File Formats

Unsigned char mdr unsigned char bdr float rtdr0

Appendices

2635A

Appendices

2635A

Waveform Comparison True RMS VS Average Responding

True RMS Measurements

Effect of Internal Noise in AC Measurements

Component

Waveform RMS CAL Hydra Only

Sine

PK-PK

Temperature Units

Scan Rate

RS-232-C Communication

Output

Hydra Memory Card Record

Index

2635A

Index

2635A