APPENDIX A Instruction List

A.1 F2MC-8FX CPU Instruction Overview

This section explains the

■

In the

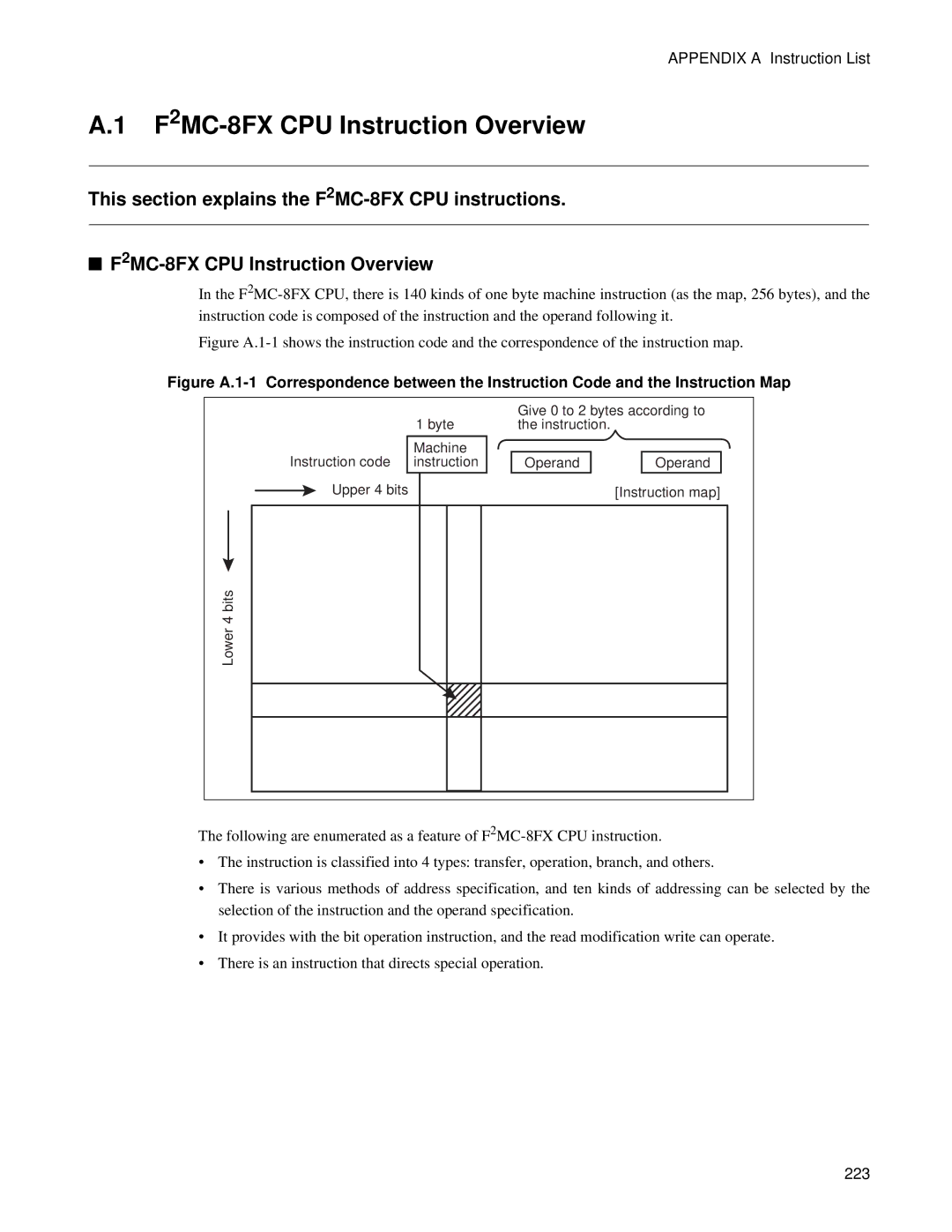

Figure A.1-1 shows the instruction code and the correspondence of the instruction map.

Figure A.1-1 Correspondence between the Instruction Code and the Instruction Map

|

| 1 byte |

|

| Machine |

Instruction code | instruction | |

| Upper 4 bits |

|

|

| |

Give 0 to 2 bytes according to the instruction.

OperandOperand

[Instruction map]

Lower 4 bits

The following are enumerated as a feature of

•The instruction is classified into 4 types: transfer, operation, branch, and others.

•There is various methods of address specification, and ten kinds of addressing can be selected by the selection of the instruction and the operand specification.

•It provides with the bit operation instruction, and the read modification write can operate.

•There is an instruction that directs special operation.

223