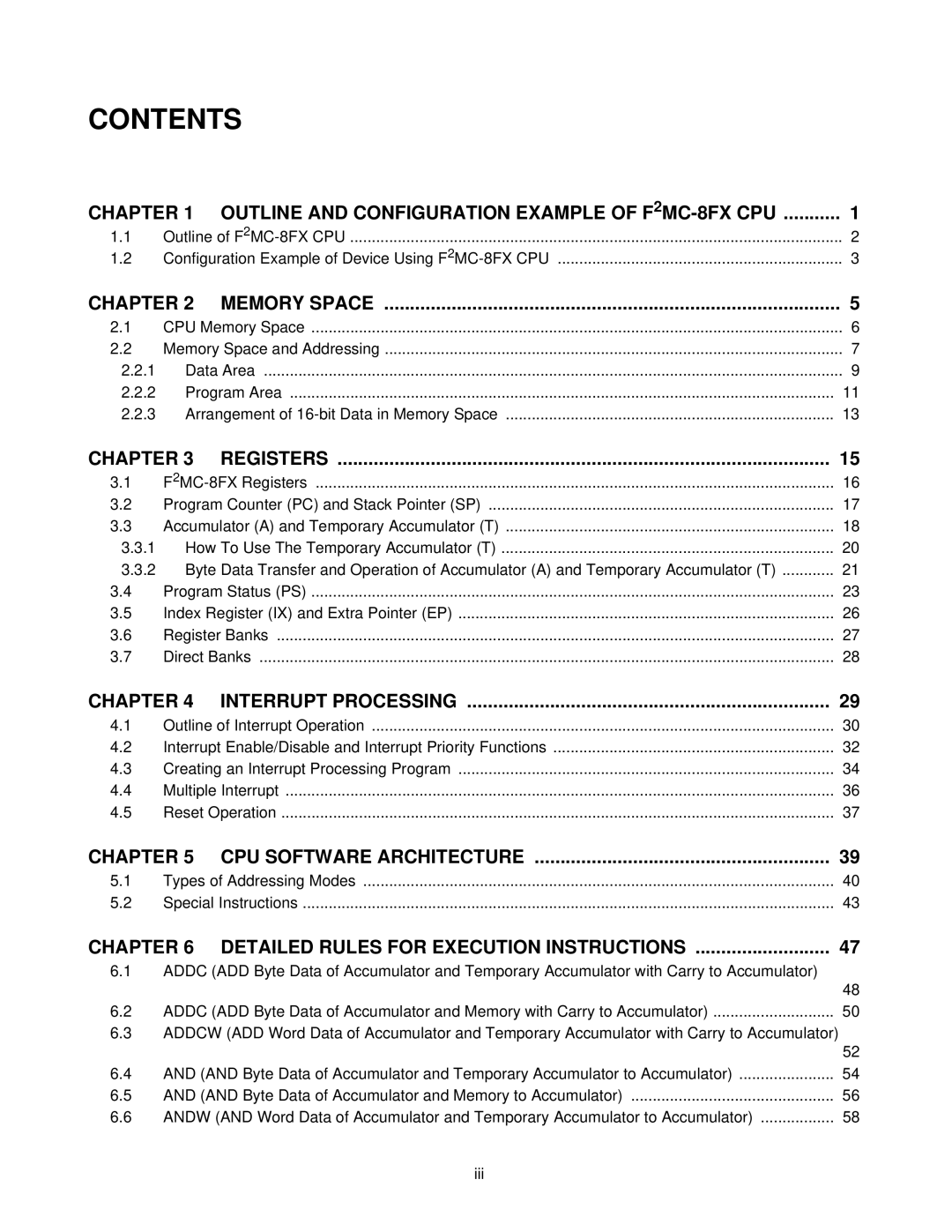

CONTENTS

CHAPTER 1 OUTLINE AND CONFIGURATION EXAMPLE OF | ........... 1 | ||

1.1 | Outline of | 2 | |

1.2 | Configuration Example of Device Using | 3 | |

CHAPTER 2 | MEMORY SPACE | 5 | |

2.1 | CPU Memory Space | 6 | |

2.2 | Memory Space and Addressing | 7 | |

2.2.1 | Data Area | 9 | |

2.2.2 | Program Area | 11 | |

2.2.3 Arrangement of | 13 | ||

CHAPTER 3 | REGISTERS | 15 | |

3.1 | 16 | ||

3.2 | Program Counter (PC) and Stack Pointer (SP) | 17 | |

3.3 | Accumulator (A) and Temporary Accumulator (T) | 18 | |

3.3.1 How To Use The Temporary Accumulator (T) | 20 | ||

3.3.2 Byte Data Transfer and Operation of Accumulator (A) and Temporary Accumulator (T) | 21 | ||

3.4 | Program Status (PS) | 23 | |

3.5 | Index Register (IX) and Extra Pointer (EP) | 26 | |

3.6 | Register Banks | 27 | |

3.7 | Direct Banks | 28 | |

CHAPTER 4 | INTERRUPT PROCESSING | 29 | |

4.1 | Outline of Interrupt Operation | 30 | |

4.2 | Interrupt Enable/Disable and Interrupt Priority Functions | 32 | |

4.3 | Creating an Interrupt Processing Program | 34 | |

4.4 | Multiple Interrupt | 36 | |

4.5 | Reset Operation | 37 | |

CHAPTER 5 CPU SOFTWARE ARCHITECTURE | 39 | ||

5.1 | Types of Addressing Modes | 40 | |

5.2 | Special Instructions | 43 | |

CHAPTER 6 DETAILED RULES FOR EXECUTION INSTRUCTIONS | 47 | ||

6.1ADDC (ADD Byte Data of Accumulator and Temporary Accumulator with Carry to Accumulator)

|

| 48 |

6.2 | ADDC (ADD Byte Data of Accumulator and Memory with Carry to Accumulator) | 50 |

6.3ADDCW (ADD Word Data of Accumulator and Temporary Accumulator with Carry to Accumulator)

|

| 52 |

6.4 | AND (AND Byte Data of Accumulator and Temporary Accumulator to Accumulator) | 54 |

6.5 | AND (AND Byte Data of Accumulator and Memory to Accumulator) | 56 |

6.6 | ANDW (AND Word Data of Accumulator and Temporary Accumulator to Accumulator) | 58 |

iii