CHAPTER 3 REGISTERS

Table

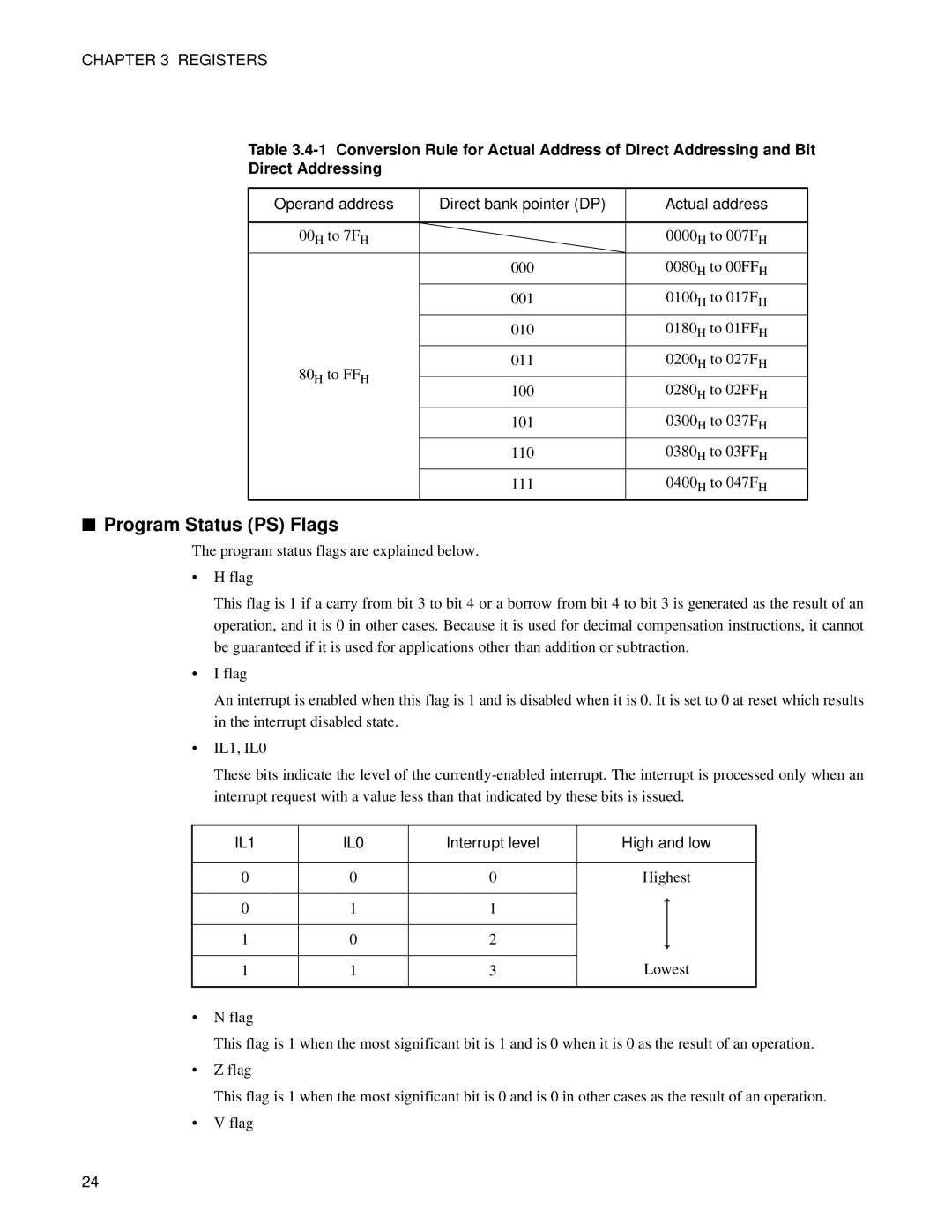

Direct Addressing

Operand address | Direct bank pointer (DP) | Actual address | |

|

|

| |

00H to 7FH |

| 0000H to 007FH | |

|

|

| |

| 000 | 0080H to 00FFH | |

|

|

| |

| 001 | 0100H to 017FH | |

|

|

| |

| 010 | 0180H to 01FFH | |

|

|

| |

80H to FFH | 011 | 0200H to 027FH | |

|

| ||

100 | 0280H to 02FFH | ||

| |||

|

|

| |

| 101 | 0300H to 037FH | |

|

|

| |

| 110 | 0380H to 03FFH | |

|

|

| |

| 111 | 0400H to 047FH | |

|

|

|

■Program Status (PS) Flags

The program status flags are explained below.

•H flag

This flag is 1 if a carry from bit 3 to bit 4 or a borrow from bit 4 to bit 3 is generated as the result of an operation, and it is 0 in other cases. Because it is used for decimal compensation instructions, it cannot be guaranteed if it is used for applications other than addition or subtraction.

•I flag

An interrupt is enabled when this flag is 1 and is disabled when it is 0. It is set to 0 at reset which results in the interrupt disabled state.

•IL1, IL0

These bits indicate the level of the

IL1 | IL0 | Interrupt level | High and low | |

|

|

|

|

|

0 | 0 | 0 | Highest | |

|

|

|

|

|

0 | 1 | 1 |

|

|

|

| |||

|

|

|

|

|

1 | 0 | 2 |

|

|

|

|

| Lowest | |

1 | 1 | 3 | ||

|

|

|

|

|

•N flag

This flag is 1 when the most significant bit is 1 and is 0 when it is 0 as the result of an operation.

•Z flag

This flag is 1 when the most significant bit is 0 and is 0 in other cases as the result of an operation.

•V flag

24