APPENDIX A Instruction List

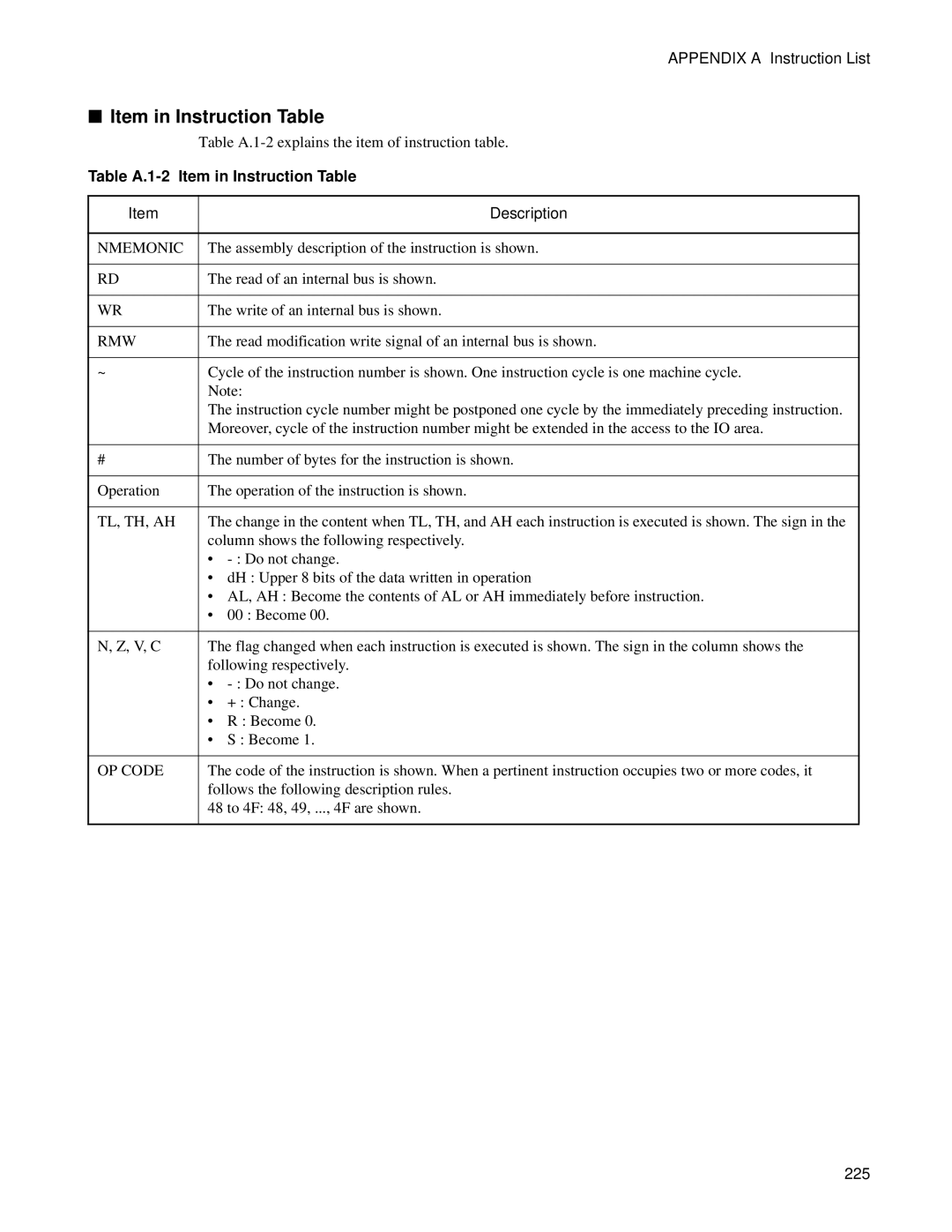

■Item in Instruction Table

Table

Table A.1-2 Item in Instruction Table

Item |

| Description |

|

| |

NMEMONIC | The assembly description of the instruction is shown. | |

|

| |

RD | The read of an internal bus is shown. | |

|

| |

WR | The write of an internal bus is shown. | |

|

| |

RMW | The read modification write signal of an internal bus is shown. | |

|

| |

~ | Cycle of the instruction number is shown. One instruction cycle is one machine cycle. | |

| Note: | |

| The instruction cycle number might be postponed one cycle by the immediately preceding instruction. | |

| Moreover, cycle of the instruction number might be extended in the access to the IO area. | |

|

| |

# | The number of bytes for the instruction is shown. | |

|

| |

Operation | The operation of the instruction is shown. | |

|

| |

TL, TH, AH | The change in the content when TL, TH, and AH each instruction is executed is shown. The sign in the | |

| column shows the following respectively. | |

| • | |

| • dH : Upper 8 bits of the data written in operation | |

| • AL, AH : Become the contents of AL or AH immediately before instruction. | |

| • | 00 : Become 00. |

|

| |

N, Z, V, C | The flag changed when each instruction is executed is shown. The sign in the column shows the | |

| following respectively. | |

| • | |

| • | + : Change. |

| • | R : Become 0. |

| • | S : Become 1. |

|

| |

OP CODE | The code of the instruction is shown. When a pertinent instruction occupies two or more codes, it | |

| follows the following description rules. | |

| 48 to 4F: 48, 49, ..., 4F are shown. | |

|

|

|

225