CHAPTER 3 REGISTERS

3.4Program Status (PS)

The program status (PS) is a

■Structure of Program Status (PS)

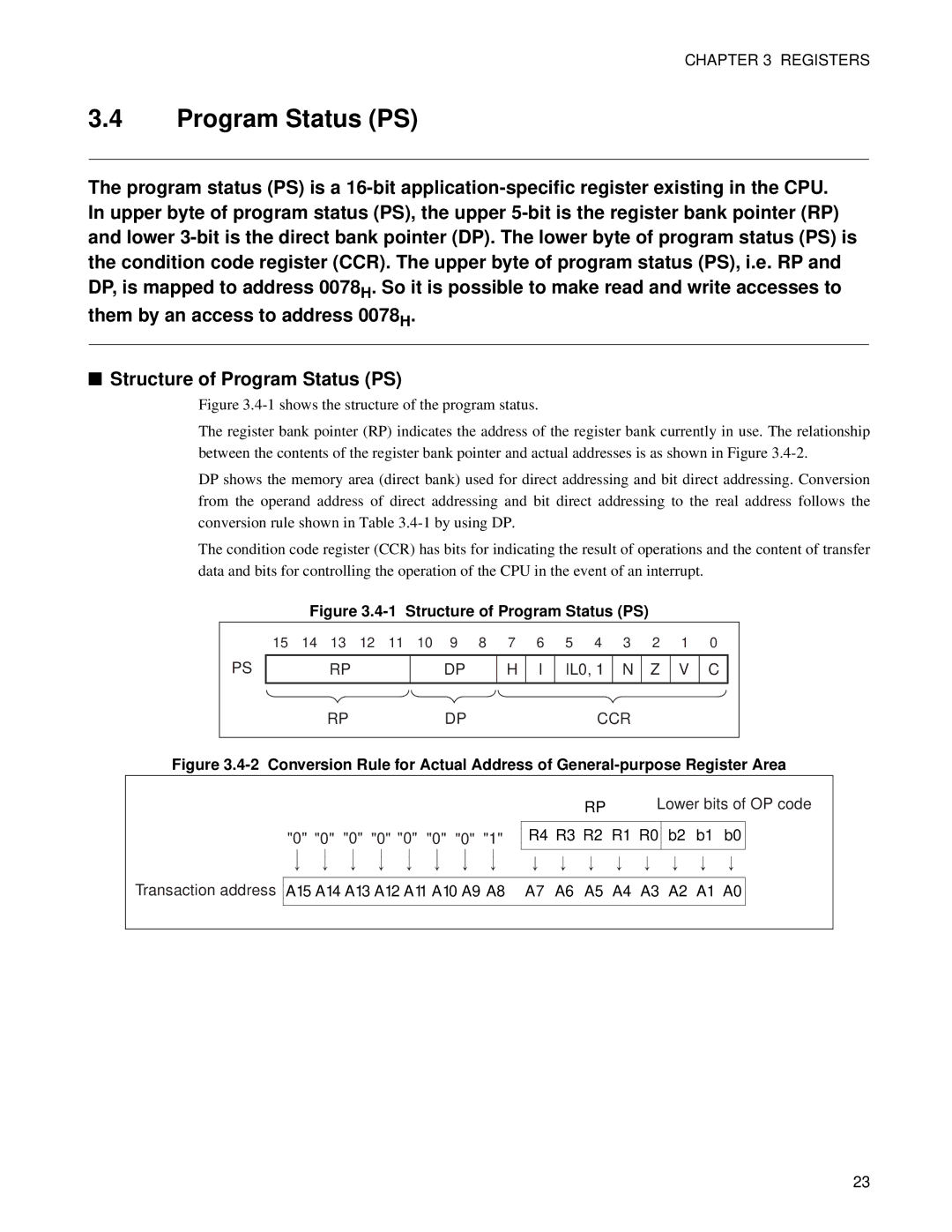

Figure 3.4-1 shows the structure of the program status.

The register bank pointer (RP) indicates the address of the register bank currently in use. The relationship between the contents of the register bank pointer and actual addresses is as shown in Figure 3.4-2.

DP shows the memory area (direct bank) used for direct addressing and bit direct addressing. Conversion from the operand address of direct addressing and bit direct addressing to the real address follows the conversion rule shown in Table 3.4-1 by using DP.

The condition code register (CCR) has bits for indicating the result of operations and the content of transfer data and bits for controlling the operation of the CPU in the event of an interrupt.

Figure 3.4-1 Structure of Program Status (PS)

15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

PS

RP

DP

H I

IL0, 1 N Z V C

RP | DP | CCR |

Figure 3.4-2 Conversion Rule for Actual Address of General-purpose Register Area

"0" "0" "0" "0" "0" "0" "0" "1"

RP | Lower bits of OP code |

R4 R3 R2 R1 R0 b2 b1 b0

Transaction address A15 A14 A13 A12 A11 A10 A9 A8 A7 A6 A5 A4 A3 A2 A1 A0

23