APPENDIX |

|

|

|

|

|

|

|

| |

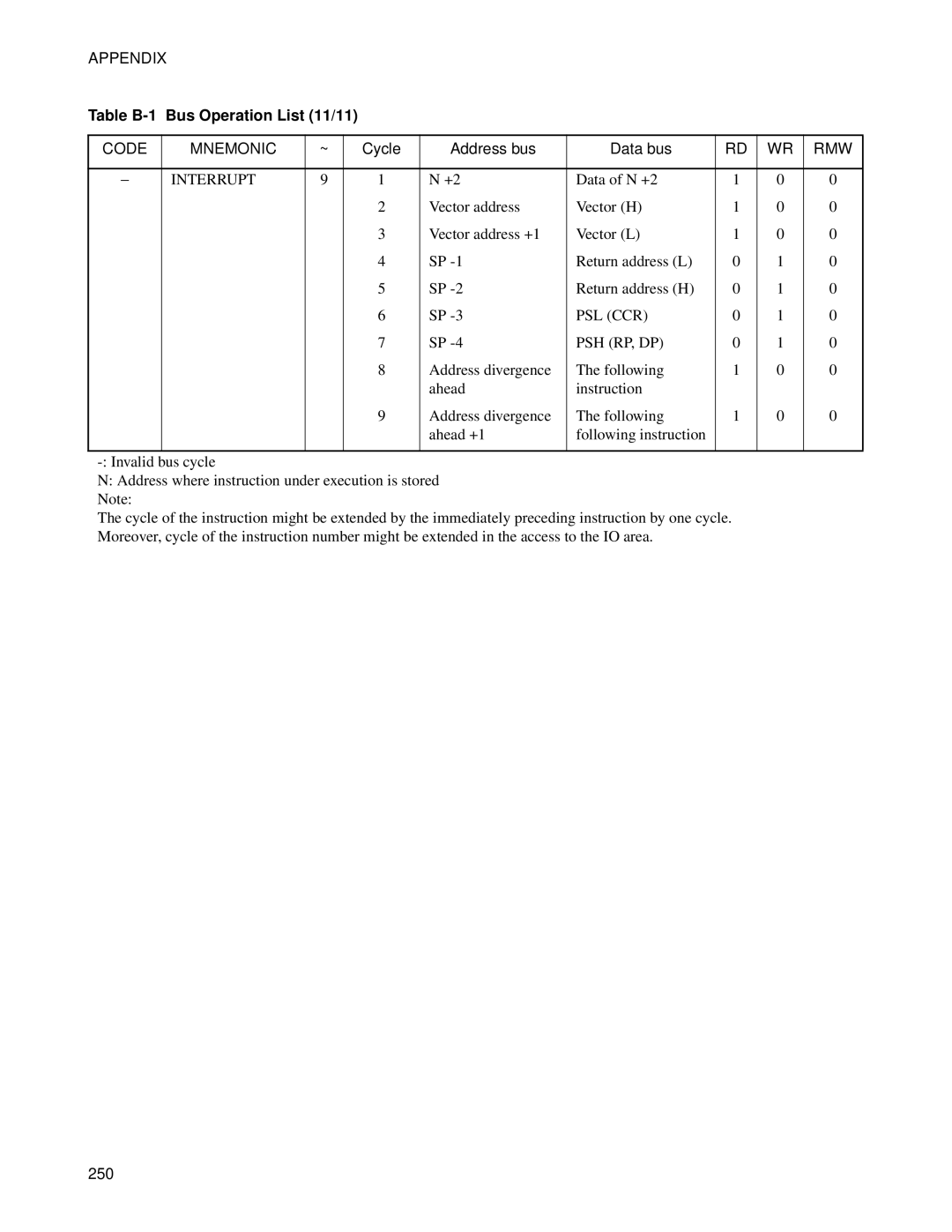

Table | Bus Operation List (11/11) |

|

|

|

|

|

| ||

|

|

|

|

|

|

|

|

|

|

CODE | MNEMONIC | ~ |

| Cycle | Address bus | Data bus | RD | WR | RMW |

|

|

|

|

|

|

|

|

|

|

− | INTERRUPT | 9 |

| 1 | N +2 | Data of N +2 | 1 | 0 | 0 |

|

|

|

| 2 | Vector address | Vector (H) | 1 | 0 | 0 |

|

|

|

| 3 | Vector address +1 | Vector (L) | 1 | 0 | 0 |

|

|

|

| 4 | SP | Return address (L) | 0 | 1 | 0 |

|

|

|

| 5 | SP | Return address (H) | 0 | 1 | 0 |

|

|

|

| 6 | SP | PSL (CCR) | 0 | 1 | 0 |

|

|

|

| 7 | SP | PSH (RP, DP) | 0 | 1 | 0 |

|

|

|

| 8 | Address divergence | The following | 1 | 0 | 0 |

|

|

|

|

| ahead | instruction |

|

|

|

|

|

|

| 9 | Address divergence | The following | 1 | 0 | 0 |

|

|

|

|

| ahead +1 | following instruction |

|

|

|

|

|

|

|

|

|

|

|

|

|

N:Address where instruction under execution is stored Note:

The cycle of the instruction might be extended by the immediately preceding instruction by one cycle. Moreover, cycle of the instruction number might be extended in the access to the IO area.

250