F2MC-8FX

Page

Fujitsu Limited

Page

Purpose and Audience

Trademark

Organization of This Manual

Copyright 2004-2008 Fujitsu Limited All rights reserved

Contents

100

253

221

Page

Changes For details, refer to main body

Main changes in this edition

Viii

Chapter Outline and Configuration Example of F2MC-8FX CPU

Outline of F2MC-8FX CPU

F2MC-8FX CPU Features

1 Configuration Example of Device Using F2MC-8FX CPU

Configuration Example of Device Using F2MC-8FX CPU

Outline and Configuration Example of F2MC-8FX CPU

This chapter explains the F2MC-8FX CPU memory space

Chapter Memory Space

1 F2MC-8FX Memory Space

CPU Memory Space

Memory Space and Addressing

1shows the memory space accessible by each addressing mode

Ffffh

Data Area

3 Example of Saving Data in Stack Area

2 Callv Jump Address Table

Program Area

Interrupt No Table address Upper data Lower data

3 Reset and Interrupt Vector Table

5 Arrangement of 16-bit Data in Memory

Arrangement of 16-bit Data in Memory Space

Memory Space

Chapter Registers

F2MC-8FX General-Purpose Registers

F2MC-8FX Registers

Stack Pointer SP

Program Counter PC and Stack Pointer SP

Temporary Accumulator T

Accumulator a and Temporary Accumulator T

XX78H

How To Use The Temporary Accumulator T

Abxxh Cdxxh RAM

9 Direct Data Transfer from Temporary Accumulator T

Direct Data Transfer from Temporary Accumulator T

1 Structure of Program Status PS

Program Status PS

IL1 IL0

Program Status PS Flags

Access to Register Bank Pointer and Direct Bank Pointer

Extra Pointer EP

Index Register IX and Extra Pointer EP

Register Banks

1 Configuration of Register Bank

Direct Banks

1 Configuration of Direct Bank

Chapter Interrupt Processing

Outline of Interrupt Operation

1 Outline of F 2MC-8FX Interrupt Operation

Interrupt Requests in Resources

Interrupt Enable/Disable and Interrupt Priority Functions

To CPU

1 Interrupt Processing Flow

Creating an Interrupt Processing Program

2 Interrupt Response Time

1 Example of Multiple Interrupt

Multiple Interrupt

Reset Operation

Interrupt Processing

This chapter explains the instructions for the F2MC-8FX CPU

Chapter CPU Software Architecture

Types of Addressing Modes

Index Addressing @IX+off

Address table upper jump address lower jump address

1 Jump Address Table

Callv #k JMP @A

Special Instructions

Divu a

Callv #k

1 Example of Using Xchw A, PC

Callv #3

Chapter Detailed Rules for Execution Instructions

Operation

Ffff H

1 Number of Execution Cycles / Byte Count / OP Code

Ffff H

Addcw a

Execution example Addcw a Memory

Assembler format Condition code CCR

Execution example and a Memory

Byte Data of Accumulator and Memory to Accumulator

Execution example and , @EP Memory

Andw a

Execution example Andw a Memory

BBC Branch if Bit is Clear

E7FE H

BBS Branch if Bit is Set

Execution example BBS 84H 0, 0FBH Memory

BC Branch relative if C=1/BLO Branch if LOwer

Execution example BC 0FEH Memory

BGE rel

Execution example BGE 02H Memory

BLT Branch Less Than zero relative if Zero

Execution example BLT 02H Memory

BN Branch relative if N =

FC5F H

BNZ Branch relative if Z = 0/BNE Branch if Not Equal

FE1E H

BNC Branch relative if C = 0/BHS Branch if Higher or Same

Execution example BNC 01H Memory

BP Branch relative if N = 0 Plus

Execution example BP 04H Memory

BZ Branch relative if Z = 1/BEQ Branch if Equal

FE1E H FE1A H

Call Call subroutine

Execution example Call 0FC00H Memory

Callv Call Vectored subroutine

Vector address VA Instruction Lower address Upper address

18-1 Call Storage Address of Vector Call Instruction

Clrb Clear direct Memory Bit

Execution example Clrb 84H Memory

Set the C-flag to Clrc Clear Carry flag

Clrc Clear Carry flag

Execution example Clrc Memory

Set the I-flag to Clri CLeaR Interrupt flag

Clri CLeaR Interrupt flag

IL1 IL0

CMP a

Execution example CMP a Memory

23-1 Number of Execution Cycles / Byte Count / OP Code

CMP CoMPare Byte Data of Accumulator and Memory

Execution example CMP 80H Memory

24-1 Number of Execution Cycles / Byte Count / OP Code

CMP CoMPare Byte Data of Immediate Data and Memory

Execution example CMP @EP , #33H Memory

Cmpw a

Execution example Cmpw Memory

DAA Decimal Adjust for Addition

26-2 Execution Example

26-1 Decimal Adjustment Table DAA

DAS Decimal Adjust for Subtraction

27-2 Execution Example

27-1 Decimal Adjustment Table DAS

DEC DECrement Byte Data of General-purpose Register

103

Decw DECrement Word Data of Accumulator

105

Decw DECrement Word Data of Extra Pointer

107

Decw DECrement Word Data of Index Pointer

109

Decw DECrement Word Data of Stack Pointer

111

Divu DIVide Unsigned

113

INC INCrement Byte Data of General-purpose Register

115

Incw INCrement Word Data of Accumulator

117

Incw INCrement Word Data of Extra Pointer

119

Incw INCrement Word Data of Index Register

121

Incw INCrement Word Data of Stack Pointer

123

JMP JuMP to address pointed by Accumulator

125

JMP JuMP to effective Address

127

MOV @A, T

129

42-1 Number of Execution Cycles / Byte Count / OP Code

MOV Move Byte Data from Memory to Accumulator

131

43-1 Number of Execution Cycles / Byte Count / OP Code

MOV Move Immediate Byte Data to Memory

133

44-1 Number of Execution Cycles / Byte Count / OP Code

MOV Move Byte Data from Accumulator to memory

135

Movw @A, T

137

46-1 Number of Execution Cycles / Byte Count / OP Code

Movw Move Word Data from Memory to Accumulator

139

Movw Move Word Data from Extra Pointer to Accumulator

141

Movw Move Word Data from Index Register to Accumulator

143

Movw A, PS

145

Movw Move Word Data from Program Counter to Accumulator

147

Movw Move Word Data from Stack Pointer to Accumulator

149

52-1 Number of Execution Cycles / Byte Count / OP Code

Movw Move Word Data from Accumulator to Memory

151

Movw Move Word Data from Accumulator to Extra Pointer

153

Movw Move Immediate Word Data to Extra Pointer

155

Movw Move Word Data from Accumulator to Index Register

157

Movw Move Immediate Word Data to Index Register

159

Movw PS, a

161

Movw Move Immediate Word Data to Stack Pointer

163

Movw Move Word data from Accumulator to Stack Pointer

165

Mulu MULtiply Unsigned

167

No operation NOP NoOPeration

NOP NoOPeration

169

Or a

171

63-1 Number of Execution Cycles / Byte Count / OP Code

Or or Byte Data of Accumulator and Memory to Accumulator

173

ORW a

175

65-1 Number of Execution Cycles / Byte Count / OP Code

Pushw Push Word Data of Inherent Register to Stack Memory

177

66-1 Number of Execution Cycles / Byte Count / OP Code

Popw POP Word Data of Intherent Register from Stack Memory

179

RET RETurn from subroutine

181

Reti RETurn from Interrupt

183

Rolc Rotate Byte Data of Accumulator with Carry to Left

185

Rorc Rotate Byte Data of Accumulator with Carry to Right

187

188

189

72-1 Number of Execution Cycles / Byte Count / OP Code

191

192

193

Setb Set Direct Memory Bit

195

Set the C-flag to Setc SET Carry flag

Setc SET Carry flag

197

Seti SET Interrupt flag

199

Swap Swap Byte Data Accumulator H and Accumulator L

201

XCH A, T

203

Xchw eXCHange Word Data Accumulator and Extrapointer

205

Xchw eXCHange Word Data Accumulator and Index Register

207

Xchw eXCHange Word Data Accumulator and Program Counter

209

Xchw eXCHange Word Data Accumulator and Stack Pointer

211

Xchw A, T

213

XOR a

215

85-1 Number of Execution Cycles / Byte Count / OP Code

217

Xorw a

219

220

Appendix

Appendix a Instruction List

F2MC-8FX CPU Instruction Overview

Table A.1-1 Sign of the Instruction List

Sign of the Instruction List

Table A.1-2 Item in Instruction Table

Item in Instruction Table

Table A.2-1 Operation List for Transfer Instructions 1/3

Operation List

Table A.2-1 Operation List for Transfer Instructions 2/3

Table A.2-2 Operation List for Operation Instructions 1/3

Table A.2-1 Operation List for Transfer Instructions 3/3

← a

Table A.2-2 Operation List for Operation Instructions 2/3

XOR A, @EP

Table A.2-2 Operation List for Operation Instructions 3/3

Table A.2-3 Operation List for Branch Instructions

Table A.2-4 Operation List for Other Instructions

Table A.3-1 Flag Change Table for Transfer Instructions 1/2

Flag Change Table

Table A.3-1 Flag Change Table for Transfer Instructions 2/2

Table A.3-2 Flag Change Table for Operation Instructions 1/3

Table A.3-2 Flag Change Table for Operation Instructions 2/3

Table A.3-2 Flag Change Table for Operation Instructions 3/3

Table A.3-3 Flag Change Table for Branch Instructions

239

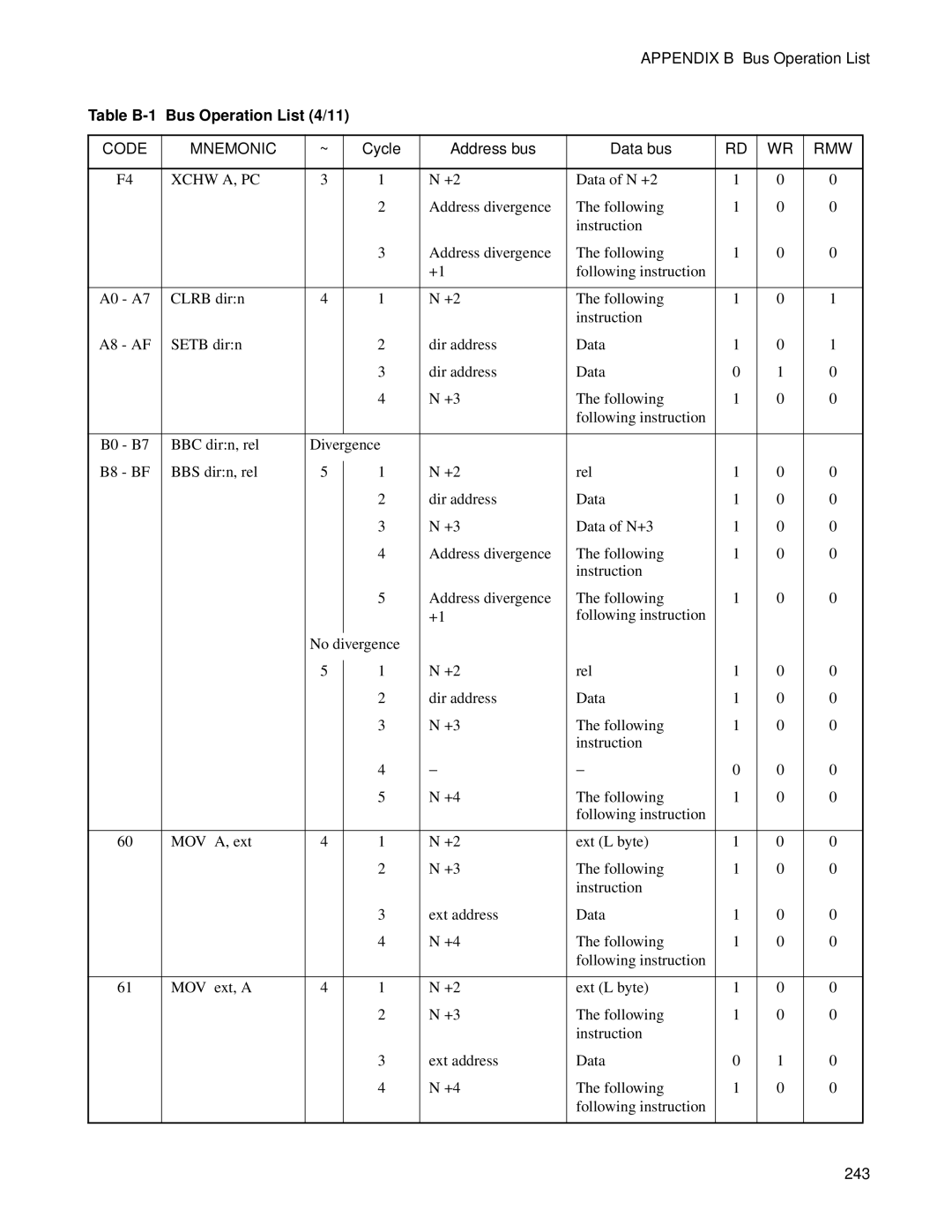

Appendix B Bus Operation List

Table B-1is a bus operation list Bus Operation List

Table B-1 Bus Operation List 1/11

Table B-1 Bus Operation List 2/11

Table B-1 Bus Operation List 3/11

Table B-1 Bus Operation List 4/11

Table B-1 Bus Operation List 5/11

Table B-1 Bus Operation List 6/11

Table B-1 Bus Operation List 7/11

DAS Rolc a Rorc a Movw A, PS Movw PS, a

Table B-1 Bus Operation List 8/11

PSL CCR

Table B-1 Bus Operation List 9/11

Table B-1 Bus Operation List 10/11

Interrupt

Table B-1 Bus Operation List 11/11

Appendix C Instruction Map

Table C-1is an instruction map Instruction Map

Table C-1 Instruction Map

252

Index

Numerics

Symbols

BLO

INC

Mulu

XCH

Fujitsu Semiconductor Controller Manual