CHAPTER 5 CPU SOFTWARE ARCHITECTURE

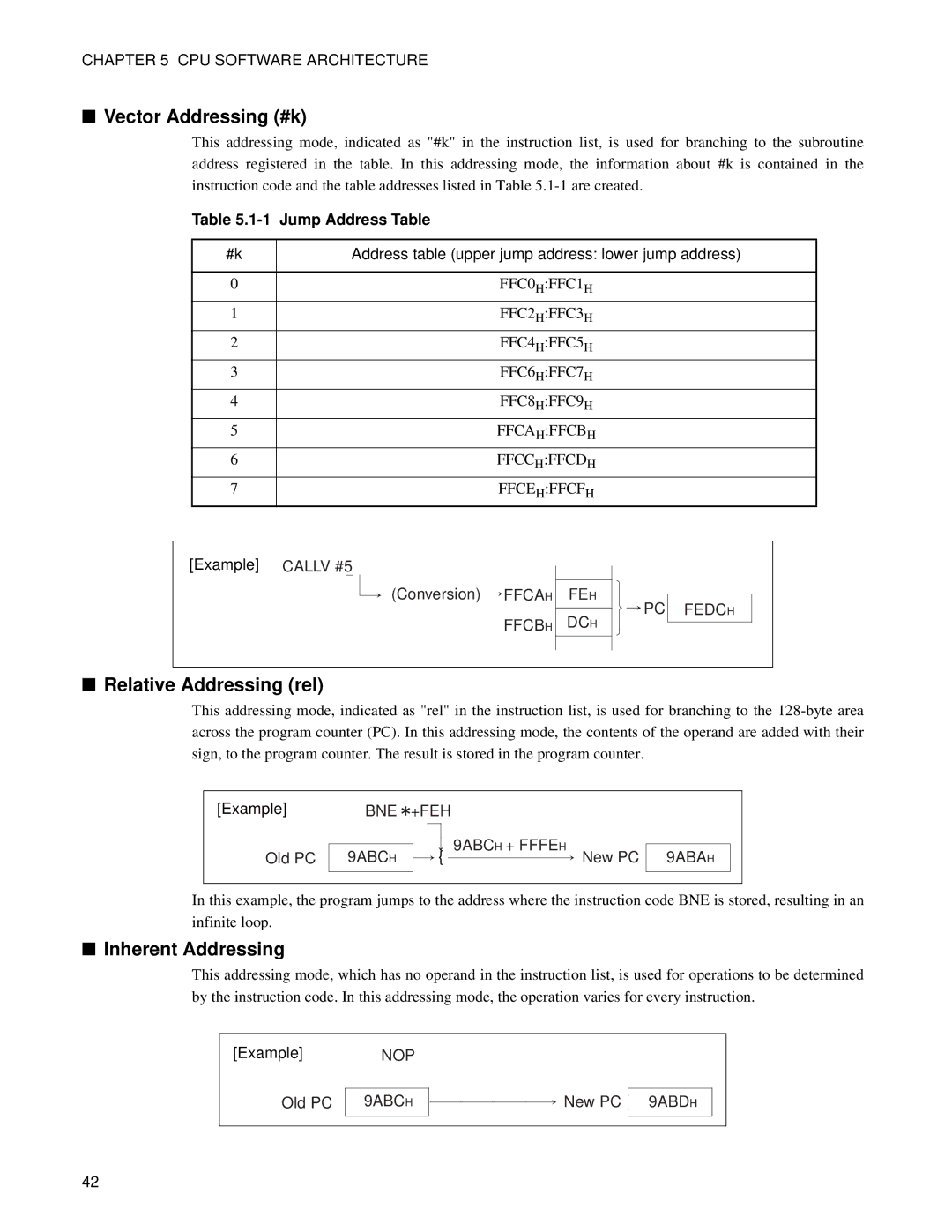

■Vector Addressing (#k)

This addressing mode, indicated as "#k" in the instruction list, is used for branching to the subroutine address registered in the table. In this addressing mode, the information about #k is contained in the instruction code and the table addresses listed in Table

Table 5.1-1 Jump Address Table

#k | Address table (upper jump address: lower jump address) |

|

|

0 | FFC0H:FFC1H |

1 | FFC2H:FFC3H |

|

|

2 | FFC4H:FFC5H |

3 | FFC6H:FFC7H |

4 | FFC8H:FFC9H |

5 | FFCAH:FFCBH |

|

|

6 | FFCCH:FFCDH |

|

|

7 | FFCEH:FFCFH |

[Example] CALLV #5

(Conversion) ![]() FFCAH

FFCAH

FFCBH

FEH

DCH

![]()

![]() PC FEDCH

PC FEDCH

■Relative Addressing (rel)

This addressing mode, indicated as "rel" in the instruction list, is used for branching to the

[Example]

Old PC

BNE | +FEH |

| |||||

|

|

|

|

|

| 9ABCH + FFFEH |

|

9ABCH |

|

|

| ||||

|

|

| { |

| New PC | ||

|

|

|

| ||||

|

|

|

|

|

|

|

|

9ABAH

In this example, the program jumps to the address where the instruction code BNE is stored, resulting in an infinite loop.

■Inherent Addressing

This addressing mode, which has no operand in the instruction list, is used for operations to be determined by the instruction code. In this addressing mode, the operation varies for every instruction.

[Example]NOP

Old PC

9ABCH

New PC

9ABDH

42