Interface

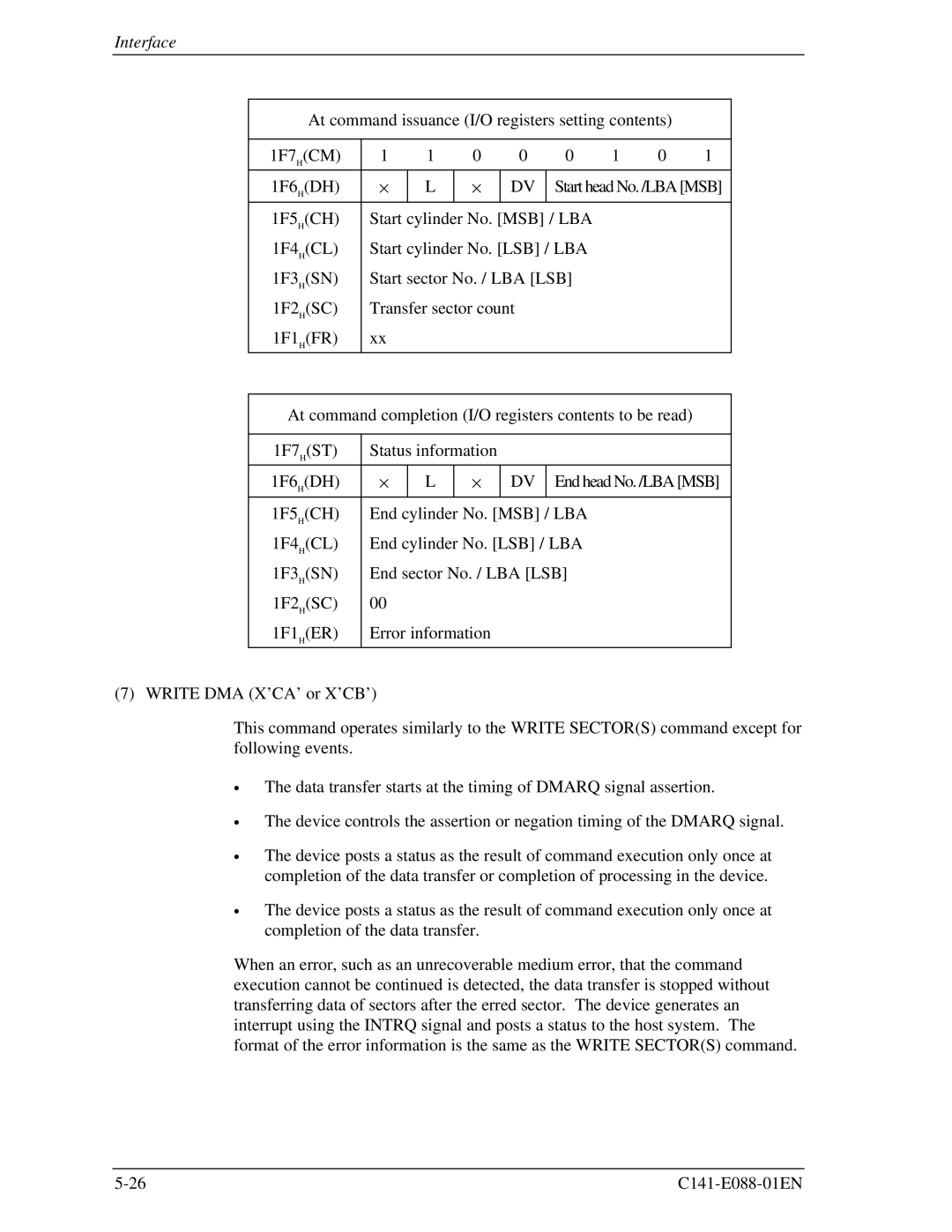

At command issuance (I/O registers setting contents)

1F7H(CM) | 1 | 1 | 0 | 0 | 0 | 1 | 0 | 1 |

1F6H(DH) | × | L | × | DV | Start head No. /LBA [MSB] | |||

|

|

|

|

|

|

|

|

|

1F5H(CH) | Start cylinder No. [MSB] / LBA |

|

|

| ||||

1F4H(CL) | Start cylinder No. [LSB] / LBA |

|

|

| ||||

1F3H(SN) | Start sector No. / LBA [LSB] |

|

|

| ||||

1F2H(SC) | Transfer sector count |

|

|

|

| |||

1F1H(FR) | xx |

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

|

At command completion (I/O registers contents to be read)

1F7H(ST) | Status information |

|

| ||

|

|

|

|

|

|

1F6H(DH) | × | L | × | DV | End head No. /LBA [MSB] |

|

|

|

|

|

|

1F5H(CH) | End cylinder No. [MSB] / LBA | ||||

1F4H(CL) | End cylinder No. [LSB] / LBA | ||||

1F3H(SN) | End sector No. / LBA [LSB] | ||||

1F2H(SC) | 00 |

|

|

|

|

1F1H(ER) | Error information |

|

| ||

|

|

|

|

|

|

(7) WRITE DMA (X’CA’ or X’CB’)

This command operates similarly to the WRITE SECTOR(S) command except for following events.

∙

∙

∙

∙

The data transfer starts at the timing of DMARQ signal assertion.

The device controls the assertion or negation timing of the DMARQ signal.

The device posts a status as the result of command execution only once at completion of the data transfer or completion of processing in the device.

The device posts a status as the result of command execution only once at completion of the data transfer.

When an error, such as an unrecoverable medium error, that the command execution cannot be continued is detected, the data transfer is stopped without transferring data of sectors after the erred sector. The device generates an interrupt using the INTRQ signal and posts a status to the host system. The format of the error information is the same as the WRITE SECTOR(S) command.