5.1 Physical Interface

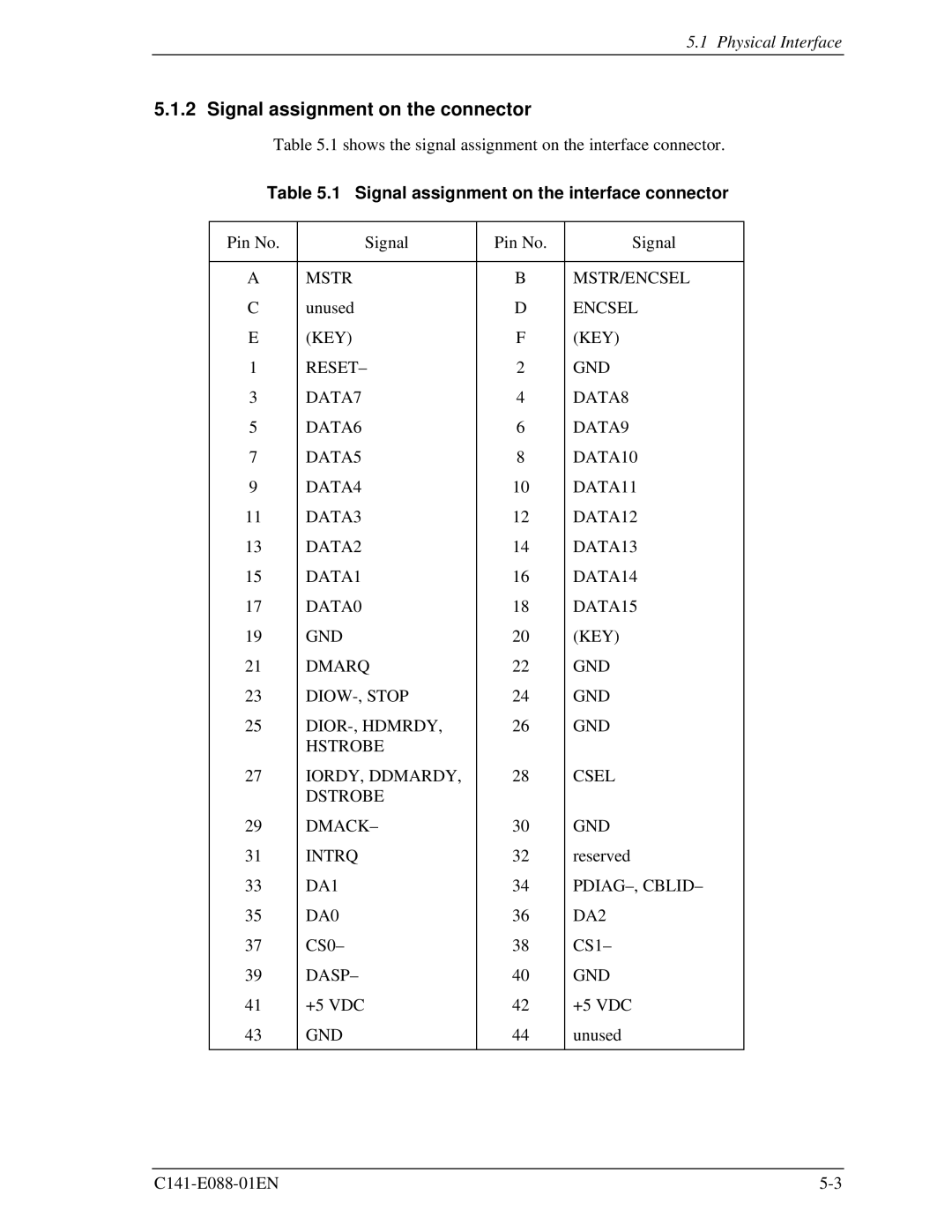

5.1.2 Signal assignment on the connector

Table 5.1 shows the signal assignment on the interface connector.

Table 5.1 Signal assignment on the interface connector

Pin No. | Signal | Pin No. | Signal |

|

|

|

|

A | MSTR | B | MSTR/ENCSEL |

C | unused | D | ENCSEL |

E | (KEY) | F | (KEY) |

1 | RESET– | 2 | GND |

3 | DATA7 | 4 | DATA8 |

5 | DATA6 | 6 | DATA9 |

7 | DATA5 | 8 | DATA10 |

9 | DATA4 | 10 | DATA11 |

11 | DATA3 | 12 | DATA12 |

13 | DATA2 | 14 | DATA13 |

15 | DATA1 | 16 | DATA14 |

17 | DATA0 | 18 | DATA15 |

19 | GND | 20 | (KEY) |

21 | DMARQ | 22 | GND |

23 | 24 | GND | |

25 | 26 | GND | |

| HSTROBE |

|

|

27 | IORDY, DDMARDY, | 28 | CSEL |

| DSTROBE |

|

|

29 | DMACK– | 30 | GND |

31 | INTRQ | 32 | reserved |

33 | DA1 | 34 | |

35 | DA0 | 36 | DA2 |

37 | CS0– | 38 | CS1– |

39 | DASP– | 40 | GND |

41 | +5 VDC | 42 | +5 VDC |

43 | GND | 44 | unused |

|

|

|

|