5.5 Ultra DMA Feature Set

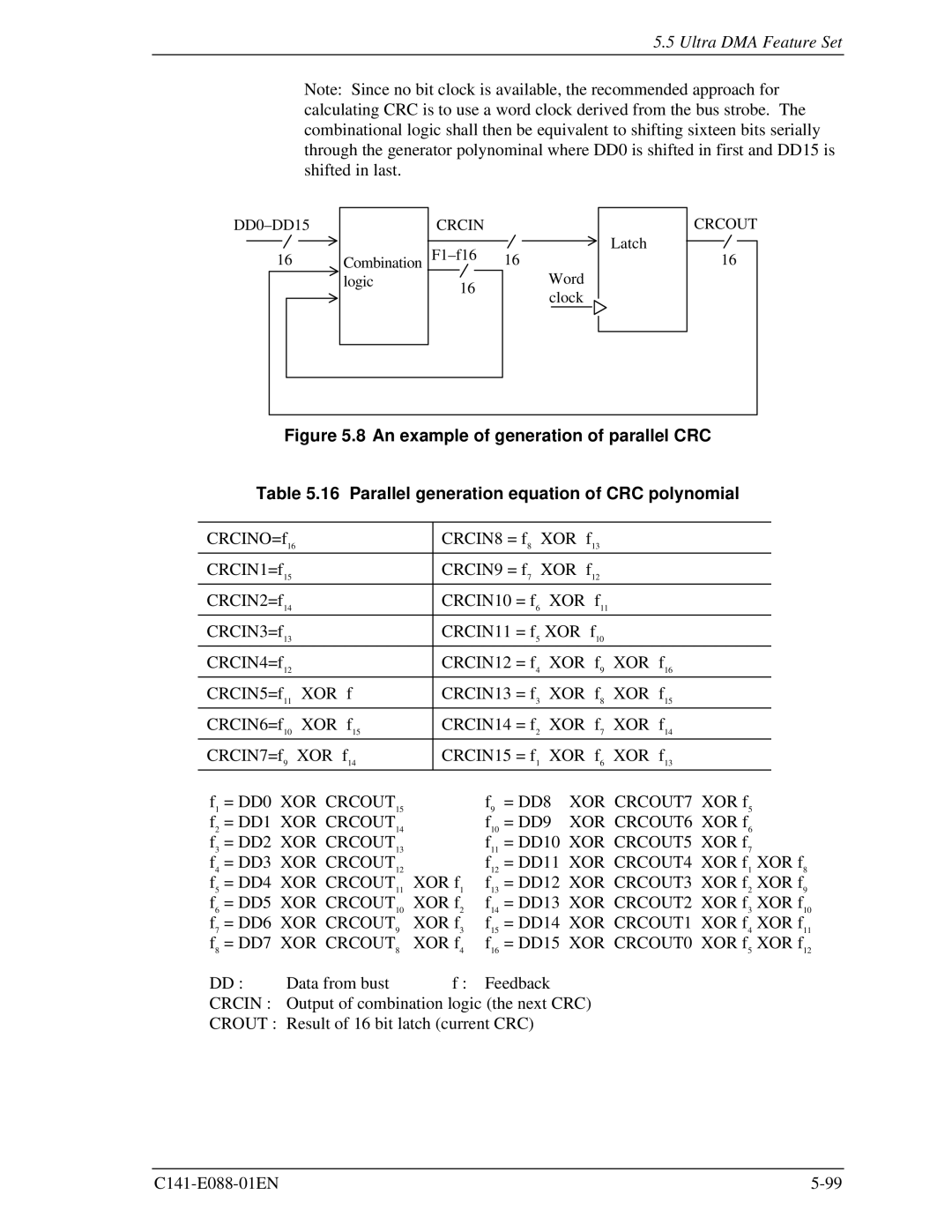

Note: Since no bit clock is available, the recommended approach for calculating CRC is to use a word clock derived from the bus strobe. The combinational logic shall then be equivalent to shifting sixteen bits serially through the generator polynominal where DD0 is shifted in first and DD15 is shifted in last.

| CRCIN |

| CRCOUT | |

|

|

| Latch | |

16 | Combination | 16 | 16 | |

| logic | 16 |

| Word |

|

|

| clock | |

|

|

|

|

Figure 5.8 An example of generation of parallel CRC

Table 5.16 Parallel generation equation of CRC polynomial

CRCINO=f16 |

| CRCIN8 = f8 | XOR f13 |

|

|

|

|

CRCIN1=f15 |

| CRCIN9 = f7 | XOR f12 |

CRCIN2=f14 |

| CRCIN10 = f6 | XOR f11 |

|

|

| |

CRCIN3=f13 |

| CRCIN11 = f5 XOR f10 | |

CRCIN4=f12 |

| CRCIN12 = f4 | XOR f9 XOR f16 |

|

|

|

|

CRCIN5=f11 | XOR f | CRCIN13 = f3 | XOR f8 XOR f15 |

CRCIN6=f10 XOR f15 | CRCIN14 = f2 | XOR f7 XOR f14 | |

|

|

|

|

CRCIN7=f9 | XOR f14 | CRCIN15 = f1 | XOR f6 XOR f13 |

|

|

|

|

f1 = DD0 XOR CRCOUT15 f2 = DD1 XOR CRCOUT14 f3 = DD2 XOR CRCOUT13 f4 = DD3 XOR CRCOUT12 f5 = DD4 XOR CRCOUT11 f6 = DD5 XOR CRCOUT10 f7 = DD6 XOR CRCOUT9 f8 = DD7 XOR CRCOUT8

| f9 | = DD8 | XOR CRCOUT7 XOR f5 |

|

| f10 | = DD9 | XOR CRCOUT6 XOR f6 |

|

| f11 | = DD10 XOR CRCOUT5 XOR f7 |

| |

| f12 | = DD11 XOR CRCOUT4 XOR f1 | XOR f8 | |

XOR f1 | f13 | = DD12 XOR CRCOUT3 XOR f2 | XOR f9 | |

XOR f2 | f14 | = DD13 XOR CRCOUT2 XOR f3 | XOR f10 | |

XOR f3 | f15 | = DD14 XOR CRCOUT1 XOR f4 | XOR f11 | |

XOR f4 | f16 | = DD15 XOR CRCOUT0 XOR f5 | XOR f12 | |

DD : Data from bust f : Feedback

CRCIN : Output of combination logic (the next CRC)

CROUT : Result of 16 bit latch (current CRC)