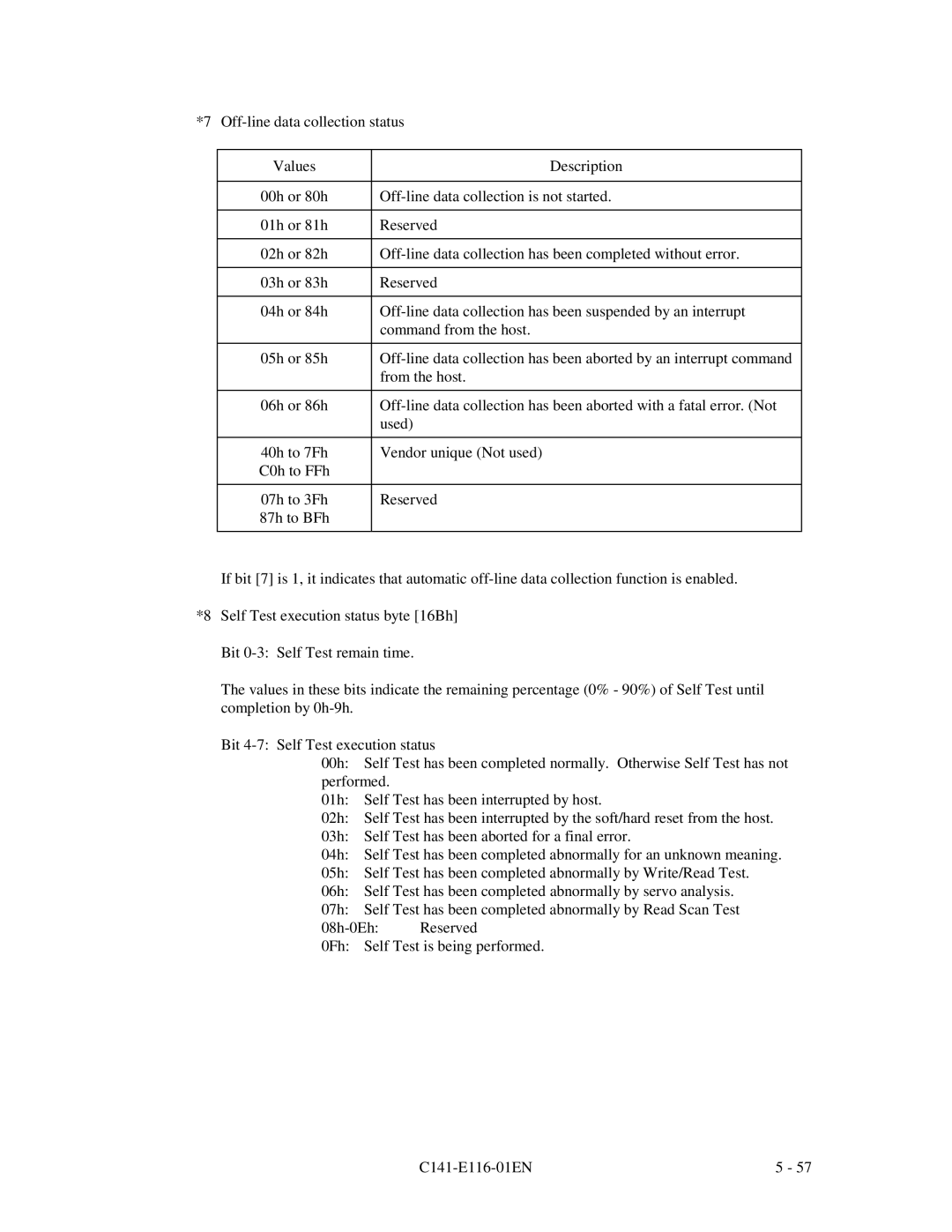

*7

Values | Description |

|

|

00h or 80h | |

|

|

01h or 81h | Reserved |

|

|

02h or 82h | |

|

|

03h or 83h | Reserved |

|

|

04h or 84h | |

| command from the host. |

|

|

05h or 85h | |

| from the host. |

|

|

06h or 86h | |

| used) |

|

|

40h to 7Fh | Vendor unique (Not used) |

C0h to FFh |

|

|

|

07h to 3Fh | Reserved |

87h to BFh |

|

|

|

If bit [7] is 1, it indicates that automatic

*8 Self Test execution status byte [16Bh]

Bit

The values in these bits indicate the remaining percentage (0% - 90%) of Self Test until completion by

Bit

00h: Self Test has been completed normally. Otherwise Self Test has not performed.

01h: Self Test has been interrupted by host.

02h: Self Test has been interrupted by the soft/hard reset from the host.

03h: Self Test has been aborted for a final error.

04h: Self Test has been completed abnormally for an unknown meaning.

05h: Self Test has been completed abnormally by Write/Read Test.

06h: Self Test has been completed abnormally by servo analysis.

07h: Self Test has been completed abnormally by Read Scan Test

0Fh: Self Test is being performed.

| 5 - 57 |